Hendrik Just

## Modeling and control of power converters in weak and unbalanced electric grids

Hendrik Just Modeling and control of power converters in weak and unbalanced electric grids The scientific series *Elektrische Energietechnik an der TU Berlin* is edited by: Prof. Dr. Sibylle Dieckerhoff Prof. Dr. Julia Kowal Prof. Dr. Ronald Plath Prof. Dr. Uwe Schäfer Elektrische Energietechnik an der TU Berlin | 12

Hendrik Just

Modeling and control of power converters in weak and unbalanced electric grids

Universitätsverlag der TU Berlin

### Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available on the Internet http://dnb.dnb.de.

## Universitätsverlag der TU Berlin, 2021

http://verlag.tu-berlin.de

Fasanenstr. 88, 10623 Berlin Tel.: +49 (0)30 314 76131 / Fax: -76133 E-Mail: publikationen@ub.tu-berlin.de

Zugl.: Berlin, Techn. Univ., Diss., 2021 Gutachterin: Prof. Dr.-Ing. Sibylle Dieckerhoff Gutachter: Prof. Dr.-Ing. Hans-Günter Eckel (Universität Rostock) Gutachter: Prof. Dr. Xavier Guillaud (Ecole Centrale de Lille, Frankreich) Die Arbeit wurde am 19. Februar 2021 an der Fakultät IV unter Vorsitz von Prof. Dr.-Ing. Julia Kowal erfolgreich verteidigt.

This work – except for quotes and where otherwise noted – is licensed under the Creative Commons License CC BY 4.0. http://creativecommons.org/licenses/by/4.0

Umschlagbild: LukaLuke Berlin | Umrichterregelung Erneuerbare Energien | CC BY 4.0

Druck: docupoint GmbH Satz/Layout: Hendrik Just

ORCID iD Hendrik Just: 0000-0003-4485-8685 http://orcid.org/0000-0003-4485-8685

ISBN 978-3-7983-3207-2 (print) ISBN 978-3-7983-3208-9 (online)

## ISSN 2367-3761 (print) ISSN 2367-377X (online)

Published online on the institutional repository of the Technische Universität Berlin: DOI 10.14279/depositonce-11674 http://dx.doi.org/10.14279/depositonce-11674 First, I would like to express my deep gratitude to my supervisor, Professor Sibylle Dieckerhoff, for her dedicated support and for her guidance towards finding my research question. Stimulating discussions and honest reviews of my results combined with the freedom to follow my own ideas continuously improved my methodology and sharpened my focus. Without her help, this research would not have been possible.

Furthermore, I want to thank Professor Hans-Günter Eckel and Professor Xavier Guillaud for their interest in my work and for being advisors for this thesis.

Special thanks go to my colleagues and friends at Technische Universität Berlin for encouraging technical discussions, fun trips, and inspiring dialogues. It was a pleasure for me to be a part of this great team. Moreover, I want to acknowledge the students who helped me to build the test benches and their extensive work during their master's theses. Particularly, I thank Immanuel Reuter, Malte Eggers, Marius Kaufmann-Bühler, and Lukas Jobb for their exceptional work and effort.

Last but not least, I want to thank my family, parents and friends for welcome distractions and mental support during my work on this thesis. I want to express my sincere gratitude to my wife Wiebke, and my children Wilhelm and Marlene for motivating me on good days and encouraging me on bad days. Their unconditional love was an invaluable support during these intense academic years. Without them this work would not have been possible at all.

Grid converters increasingly affect power system operation due to the increasing share of renewable energy sources and less conventional power plants with synchronous machines connected to the grid. This shift in power generation leads to converter-dominated weak grids, which show critical stability phenomena but also enable converters to contribute to grid stability and voltage support actively. The interaction between converters and the power system is predominantly affected by the converter control, which must handle even severe operational scenarios such as unbalanced faults that require sophisticated control schemes and modeling techniques.

Grid-following and grid-forming converter controls have attracted much attention in previous research, and various sophisticated control schemes for grid converters have been developed. However, these control schemes are mainly analyzed and designed with small-signal models showing insufficient accuracy for severe transient processes such as unbalanced grid faults. Accordingly, large-signal dynamics and transient stability phenomena of grid converters are rarely addressed in the literature. In order to assess transient stability, recent research started to analyze simplified mature converter controls in weak grids that may not sufficiently represent real systems with state-of-the-art controllers. Consequently, this thesis focuses on modeling and control of grid converters in weak grids and during unbalanced faults considering large-signal dynamics and transient stability of sophisticated control schemes. The main objectives are: (i) identify critical operational scenarios and interactions of converters with the electric grid; (ii) improve the control structures and their design; (iii) develop analysis techniques to assess large-signal dynamics and transient stability.

The Phase-Locked Loop (PLL) is identified as critical controller part of grid-following controls that predominantly affects converter control performance and stability during grid faults. In order to predict the fault dynamics, a model is derived that describes the coupling of PLLs with the converter current control. Based on this model, it is proved that conventional worst-case scenarios are not representing the worst-case for converter controls, and thus they are redefined in this thesis. Then, the control requirements are extracted from the grid codes, and an extended design process based on small-signal models is proposed. This process shows improved control performance in comparison to the conventional designs but also reveals that some PLLs with prefilter are prone to transient instability. For these PLLs,

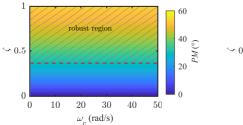

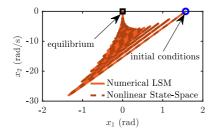

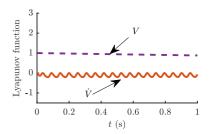

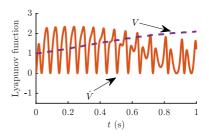

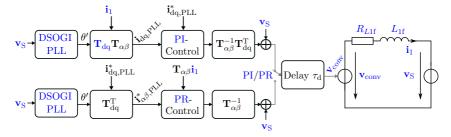

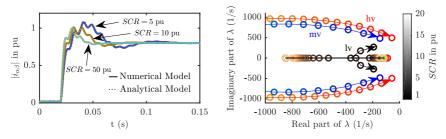

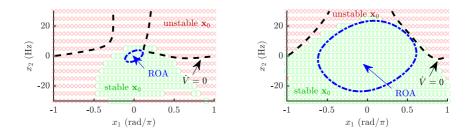

a multi-fidelity design process using large-signal and small-signal models is proposed, which identifies empirically the unstable design space that cannot be predicted by the small-signal model. To assess the transient stability analytically, a PLL with prefilter is analyzed with Lyapunov's direct method, and an analytical stability criterion for the design parameters is derived. Based on Lassalle's invariance principle, a Lyapunov function is proposed to determine the stable state-space region for grid-following converters in weak grids, which indicates that particularly weak inductive grids are prone to instability of the converter control during grid voltage transients.

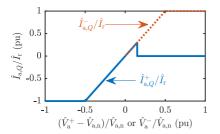

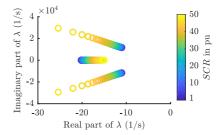

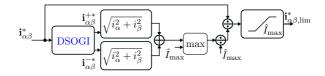

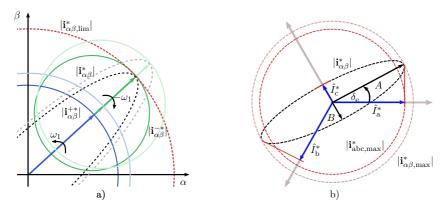

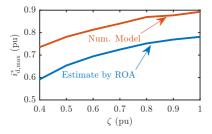

The most severe grid voltage transients occur during faults that require dual sequence current control to achieve different objectives such as rejecting active power oscillation or supporting the grid voltage. The dominant indicators for these objectives are derived, and a current reference generator is proposed that achieves satisfactory results for realizing both objectives simultaneously. The current reference generator is combined with a current and voltage limitation that shows improved dynamics without suffering from distortions in the steady-state and conserves the control objective during unbalanced grid faults. Current reference generators have a large impact on the stability, so the minimum short-circuit ratio is determined for which the system is stable, indicating that grid-following controls can be used in weak grids while showing insufficient stability for very weak grids.

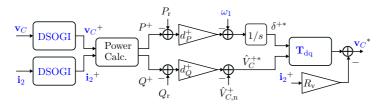

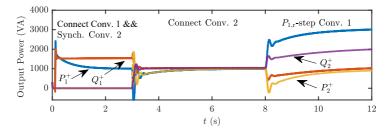

Grid-forming controls enable converters to operate stably in very weak grids, and they can also achieve control objectives during unbalanced faults regarding power oscillations and grid voltage support. Accordingly, a voltage reference generator for the negative sequence of the droop control is proposed that rejects the active power oscillations. The control performance is compared with a voltage support scheme to show the trade-off between rejecting active power oscillations and supporting grid voltages.

These results and findings are experimentally validated with three different test benches introduced in this thesis.

Based on the findings, the main conclusions of this research are: First, converters must be evaluated in different worst-case operational scenarios than conventional generation units. Second, PLLs should be designed considering the current control by taking into account critical transient stability phenomena in weak grids and during severe grid faults. Therefore, nonlinear analysis techniques are crucial to assess large-signal dynamics and transient stability. Third, grid-following controls can only be used to a minimum short-circuit ratio that is affected by the converter control scheme and its design. Fourth, grid-forming controls can be stable even in very weak grids and are also able to provide comprehensive grid services during unbalanced faults. Consequently, converter-dominated grids in the current state should rely on both grid-following and grid-forming converters to safely operate during weak and stiff grid conditions.

## Kurzfassung

Der steigende Anteil an erneuerbaren Energien in den Energieversorgungsnetzen führt zu der Verdrängung konventioneller Kraftwerke basierend auf Synchrongeneratoren, die direkt mit dem Netz verbunden sind. Diese Entwicklung lässt umrichterdominierte und schwache Netzabschnitte entstehen, die kritischen Stabilitätsmechanismen unterliegen, allerdings auch ermöglichen, dass Umrichter aktiv zur Netzstützung und Netzstabilität beitragen können. Vor allem die Umrichterregelung hat einen signifikanten Einfluss auf die Wechselwirkung mit dem Netz und muss den sicheren Betrieb jederzeit gewährleisten, was vor allem in schwachen Netzen und während unsymmetrischer Netzfehler eine Herausforderung darstellt.

Die aktuelle Forschung im Bereich Netzumrichterregelung arbeitet an der Weiterentwicklung von netzfolgenden und netzbildenden Regelungsstrukturen. Meistens werden diese Regelungen mit Kleinsignal-Modellen analysiert und ausgelegt, die vor allem bei kritischen Netzfehlern keine hinreichende Genauigkeit erzielen. Das Großsignalverhalten wird meistens nicht in die Auslegung der Regelung mit einbezogen und die Untersuchung der transienten Stabilität nur exemplarisch mit Zeitbereichssimulationen durchgeführt. Es existieren erste Untersuchungen der transienten Stabilität von Umrichtern in schwachen Netzen. Diese basieren allerdings auf vereinfachten Regelungsstrukturen, die für reale Systeme nur unzureichend anwendbar sind. Um die genannten Lücken zu schließen, beschreibt die vorliegende Arbeit die Modellierung und Regelung von Netzumrichtern in schwachen Netzen und während unsymmetrischer Netzfehler unter Einbeziehung des Großsignalverhaltens und moderner Regelungsstrukturen. Die Hauptziele dieser Arbeit sind: (i) Identifizierung kritischer Betriebsszenarien bei der Interaktion von Umrichtern mit dem Netz; (ii) Weiterentwicklung der Regelungsstrukturen mit zugehörigen Auslegungskriterien; (ii) Erforschung von Analysemethoden zur Bewertung des Großsignalverhaltens und der transienten Stabilität.

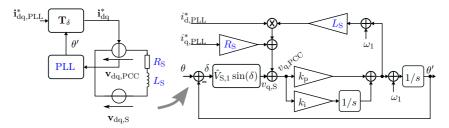

In dieser Arbeit wird die Phase-Locked Loop (PLL) als elementare Regelungskomponente identifiziert, die die netzfolgende Umrichterregelung vor allem während Netzfehlern signifikant beeinflusst. Um dieses Verhalten beschreiben zu können, wird ein Simulationsmodell vorgestellt, welches die Kopplung zwischen Stromregelung und PLL beschreibt. Dieses Modell zeigt, dass die konventionellen Worst-Case Betriebsszenarien im Netz nicht für Umrichter gültig sind und angepasst werden müssen. Basierend auf dem Modell und den angepassten Betriebsszenarien, werden die Netzanforderungen für Umrichter aus den Netznormen diskutiert und eine Reglerauslegung basierend auf Kleinsignalmodellen vorgestellt. Die vorgeschlagene Auslegung führt zu einem schnelleren Ausregelvorgang als konventionelle Auslegungsansätze. Allerdings sind einige PLLs mit Vorfilter während kritischer Netzfehler instabil, da das Kleinsignalmodell für diese nur unzureichend genau ist. Aus diesem Grund wird ein Multi-fidelity Auslegungsprozess vorgestellt. Dieser basiert auf Kleinsignal- und Großsignalmodellen, wobei das Großsignalmodell empirisch die Auslegungsparameter identifiziert, die zur transienten Instabilität führen. Um die transiente Stabilität analytisch zu untersuchen, werden die PLLs mit Lyapunov's Direct Method analysiert. Dies führt zu einem analytischen Stabilitätskriterium für PLLs mit Vorfilter. Darauf aufbauend wird mit Hilfe Lasalle's Invariance Principle eine Lyapunov-Funktion berechnet, die für netzfolgenden Umrichter in schwachen Netzen die stabile Region im Zustandsraum ermittelt. Diese Untersuchung zeigt, dass vor allem Umrichter in schwachen, induktiven Netzen durch transiente Vorgänge in den Netzspannungen instabil werden können.

Netzfehler führen zu den kritischsten transienten Vorgängen. Vor allem unsymmetrische Netzfehler setzen voraus, dass der Umrichter zuverlässig den Mit- und Gegensystemstrom regeln kann. Aus diesem Grund wird eine Regelung vorgestellt, die den Strom in beiden Systemen regelt und zusätzlich bei Netzfehlern Wirkleistungsoszillationen minimiert oder die Netzspannung stützt. Dazu werden Stromsollwertberechnungen präsentiert, um diese Regelungsziele zu erreichen. Diese werden mit einer Strom- und Spannungsbegrenzung kombiniert, die die Unterdrückung der Leistungsoszillationen nicht verhindert und das dynamische Regelungsverhalten verbessert, ohne dabei zu zusätzlichen Verzerrungen im stationären Bereich zu führen. Darüber hinaus hat die Stromsollwertberechnung einen großen Einfluss auf die Stabilität. Um dies zu untersuchen, wird die minimal notwendige Netzkurzschlussleistung für einen stabilen Betrieb ermittelt. Das Ergebnis zeigt, dass netzfolgende Umrichter stabil in schwachen Netzen betrieben werden können, allerdings sehr schwache Netze wahrscheinlich zur Instabilität führen.

Netzbildende Regelung ermöglichen den Umrichterbetrieb in sehr schwachen Netzen und können darüber hinaus auch bei unsymmetrischen Netzfehlern die Wirkleistungsoszillationen unterdrücken oder die Netzspannungen stützen. Dafür wird eine Spannungssollwertberechnung für die Droop-Regelung vorgestellt, die die Wirkleistungsoszillationen unterdrückt. Der Vergleich mit einem Regelungskonzept für Netzspannungsstützung zeigt, dass die beiden Regelungsziele nicht simultan erreicht werden können, sodass deren Anwendung davon abhängt welches der beiden Regelungsziele eine höhere Priorität hat.

Die präsentierten Modelle und Ergebnisse sind mit Hilfe von drei entwickelten Prüfaufbauten experimentell validiert worden.

Basierend auf diesen Erkenntnissen, können folgende Schlussfolgerungen gezogen werden: Erstens, für Umrichter ergeben sich andere Worst-Case Betriebsszenarien als für konventionelle Generatoren am Netz. Dies muss vor allem bei der Auslegung und Bewertung der Regelung beachtet werden. Zweitens, PLLs müssen unter Berücksichtigung der Stromregelung ausgelegt werden, wobei zusätzlich die transiente Stabilität in schwachen Netzen und bei kritischen Netzfehlern mitberücksichtigt werden muss. Dafür müssen durch die Struktur der Umrichterregelung vor allem Analyseverfahren für nichtlineare Systeme zum Einsatz kommen. Drittens, netzfolgende Umrichter können einen stabilen Betrieb nur bis zu einer bestimmten minimalen Netzkurzschlussleistung gewährleisten, die maßgeblich von der Regelungsstruktur und der Stromsollwertberechnung abhängig ist. Viertens, für sehr schwache Netze sollten netzbildende Regelungen eingesetzt werden, um das System stabil zu halten. Diese können darüber hinaus auch zusätzliche Netzdienstleistungen während unsymmetrischer Fehlerfälle bereitstellen. Es ist davon auszugehen, das umrichterbasierte Netzabschnitte im derzeitigen Stadium von netzfolgenden als auch netzbildenden Umrichter profitieren, um bei hohen als auch bei kleinen Kurschlussleistungen stabil betrieben werden zu können.

## Contents

|   |            |                 | ns                                                                 |    |

|---|------------|-----------------|--------------------------------------------------------------------|----|

| 1 | Intr       | oducti          | on                                                                 | 1  |

| 2 |            | tical C<br>ough | onverter Properties Concerning Weak Grids and Fault Ride-          | 3  |

|   | 2.1        | <u> </u>        | Converter Operation                                                | 4  |

|   | 2.1        |                 | ized Converter Utilization                                         | 7  |

|   | 2.2        |                 | Voltage Support                                                    | 8  |

|   | 2.3<br>2.4 |                 | Structure and Contributions                                        | 9  |

| 3 | The        | oretica         | al Framework                                                       | 13 |

|   | 3.1        | Power           | Electronics in Power Systems                                       | 13 |

|   |            | 3.1.1           | Power System Model                                                 | 13 |

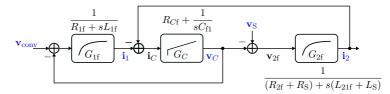

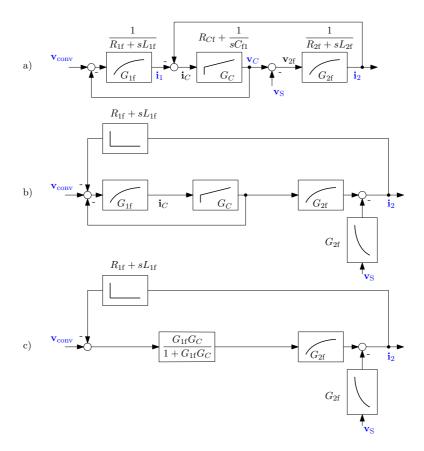

|   |            | 3.1.2           | 2-Level Converter with LCL-Filter                                  | 17 |

|   | 3.2        |                 | rs, Space Vectors and Symmetrical Components to Describe Grid Con- |    |

|   |            | verter          | Dynamics during Faults                                             | 18 |

|   |            | 3.2.1           | Positive, Negative and Zero-Sequence in abc-Frame                  | 18 |

|   |            | 3.2.2           | Positive, Negative and Zero-Sequence in $\alpha\beta$ -Frame       | 20 |

|   |            | 3.2.3           | Positive, Negative and Zero-Sequence in dq-Frame                   | 22 |

|   | 3.3        | Grid V          | Voltage Characteristics and Faults                                 | 24 |

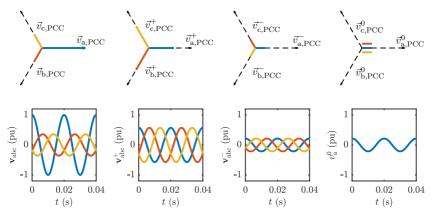

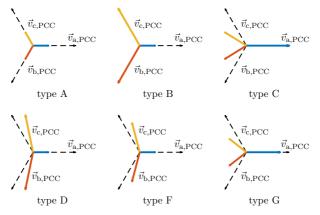

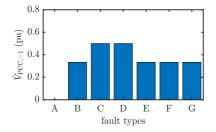

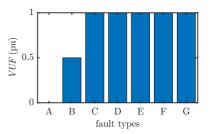

|   |            | 3.3.1           | Definition and Characterization of Fault Types                     | 25 |

|   |            | 3.3.2           | Fault Ride-Through (FRT)                                           | 29 |

|   |            | 3.3.3           | Grid Operating Range and Voltage Harmonics                         | 31 |

|   | 3.4        | Feedba          | ack Control for Grid Converters                                    | 32 |

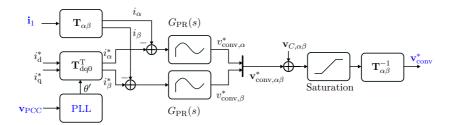

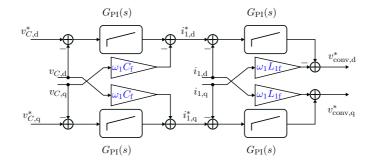

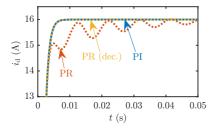

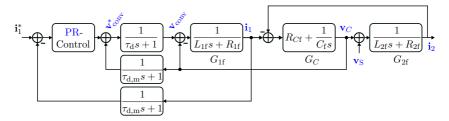

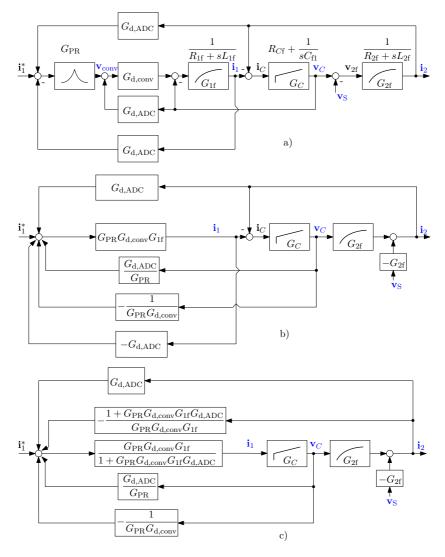

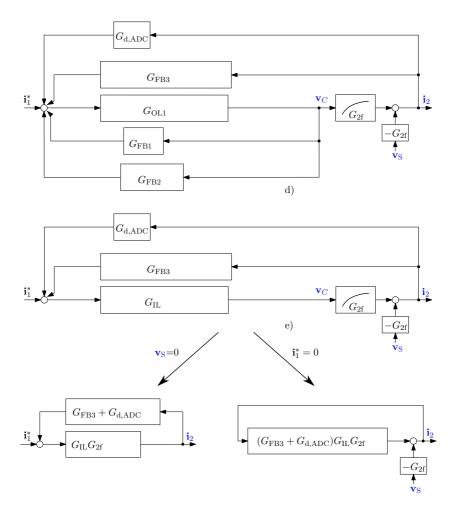

|   |            | 3.4.1           | Voltage Oriented Control with PI- and PR-controllers               | 33 |

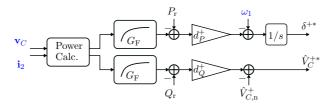

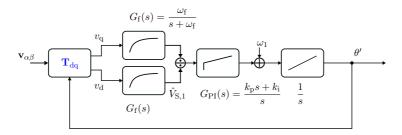

|   |            | 3.4.2           | Grid-forming Converter Control: Droop-Control                      | 35 |

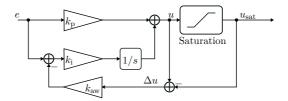

|   |            | 3.4.3           | Peak Current and Peak Voltage Limitation with Anti-Windup          | 37 |

| 4 |            | ulatio          | a and Rapid Control Prototyping Framework for Grid Convert-        |    |

|   | ers        | a               |                                                                    | 39 |

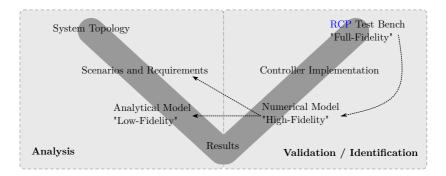

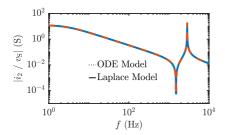

|   | 4.1        |                 | ation - Multi-Fidelity Modeling Approach                           | 40 |

|   |            | 4.1.1           | Numerical Models - Large-Signal Models                             | 40 |

|   |            | 4.1.2           | Nonlinear Time-Invariant - Large-Signal Models                     | 41 |

## Contents

|   |     | 4.1.3 Linear Time-Invariant Models - Small-Signal Models                     | 42  |

|---|-----|------------------------------------------------------------------------------|-----|

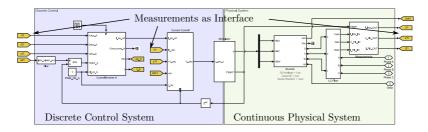

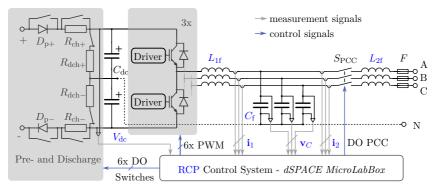

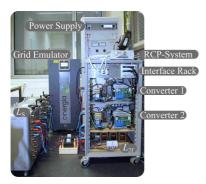

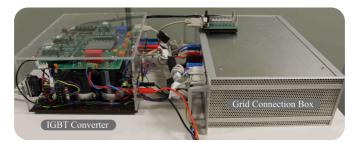

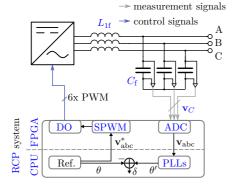

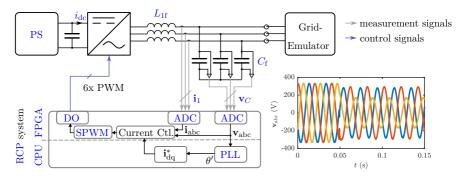

|   | 4.2 | Grid Converter Test Bench with Rapid Control Prototyping                     | 46  |

|   |     | 4.2.1 Basic Concept: Converter Prototypes with Rapid Control Prototyping     |     |

|   |     | and Grid Emulation                                                           | 47  |

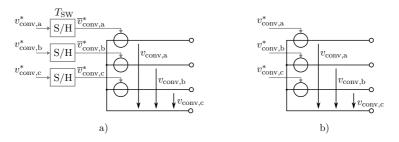

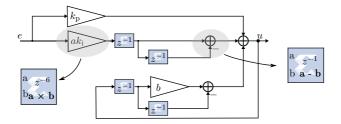

|   |     | 4.2.2 Generic Controller Implementation                                      | 53  |

| 5 | Mo  | deling, Design, and Characterization of Phase-Locked-Loops during            |     |

|   | Gri | d Faults                                                                     | 57  |

|   | 5.1 | Converter Control Requirements and Worst-Case Grid Scenarios considering     |     |

|   |     | Severe Network Disturbances and Converter Fault Current Injection            | 64  |

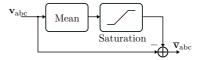

|   | 5.2 | Control and Disturbance Characterization of Online Symmetrical Component     |     |

|   |     | Decomposition                                                                | 68  |

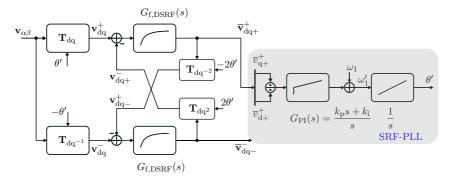

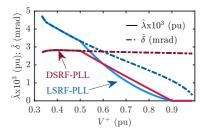

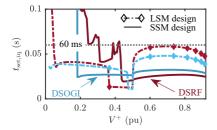

|   |     | 5.2.1 Dual Synchronous Reference Frame (DSRF)                                | 69  |

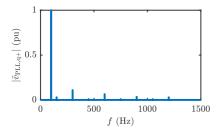

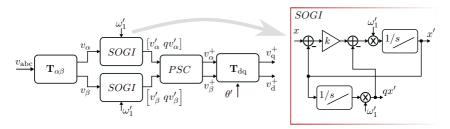

|   |     | 5.2.2 Dual Second Order Generalized Integrator (DSOGI)                       | 71  |

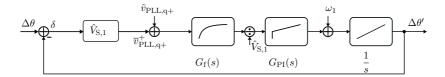

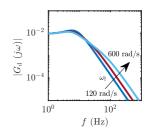

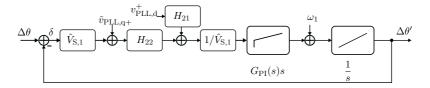

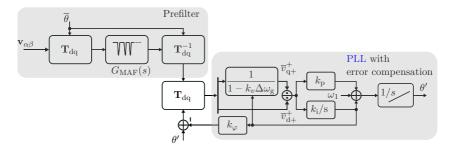

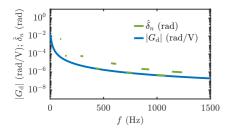

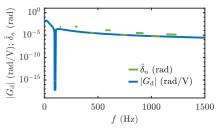

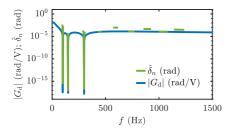

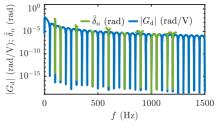

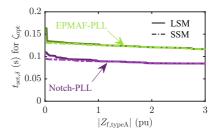

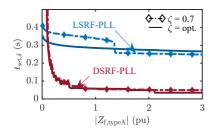

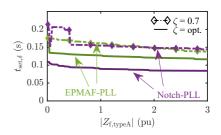

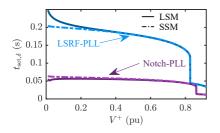

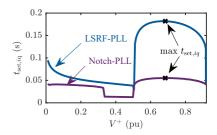

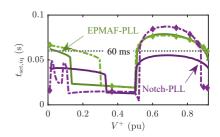

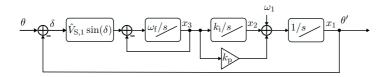

|   | 5.3 | Control and Disturbance Characterization for PLLs with Prefilters            | 73  |

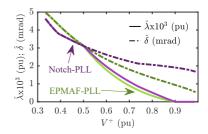

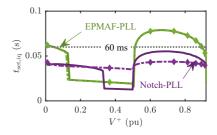

|   |     | 5.3.1 Notch-filter (Nf)                                                      | 74  |

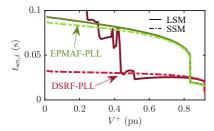

|   |     | 5.3.2 $$ Enhanced Moving Average Filter with Prefiltering Stage (EPMAF) $$ . | 75  |

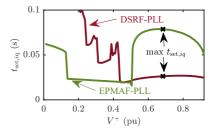

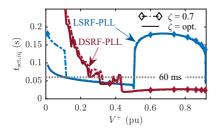

|   | 5.4 | PLL Control Bandwidth Design based on the Required Distortion Attenuation    |     |

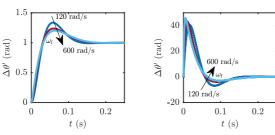

|   |     | utilizing Small-Signal Models (SSMs)                                         | 77  |

|   |     | 5.4.1 Is the Symmetrical Optimum Applicable for Prefiltered Synchronous      |     |

|   |     | Reference Frame (SRF)-PLLs?                                                  | 79  |

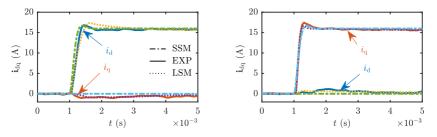

|   |     | 5.4.2 Small-Signal Model (SSM)-based Design of PLLs utilizing the Symmet-    |     |

|   |     | rical Optimum (SO)                                                           | 82  |

|   | 5.5 | PLL Model Validation with Rapid Control Prototyping (RCP)-System and         |     |

|   |     | SiC Converter Prototype                                                      | 88  |

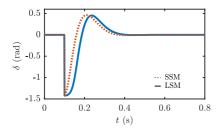

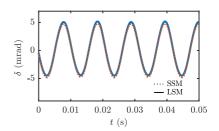

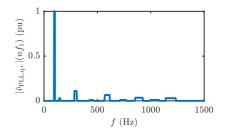

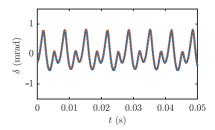

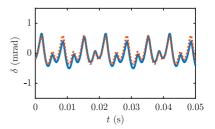

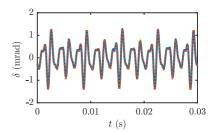

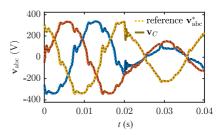

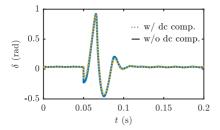

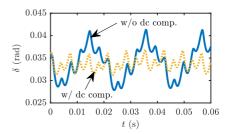

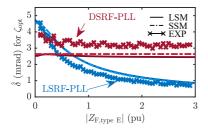

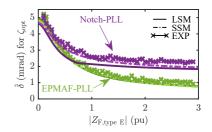

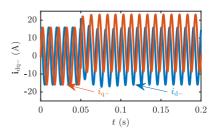

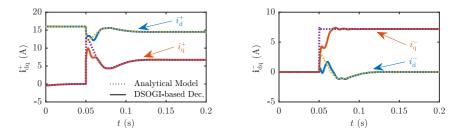

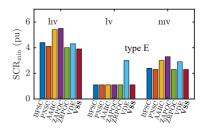

|   |     | 5.5.1 Steady-State Distortion Rejection during Type E Faults                 | 90  |

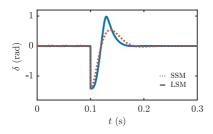

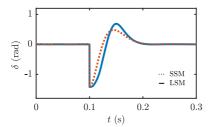

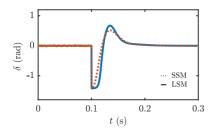

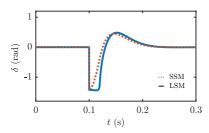

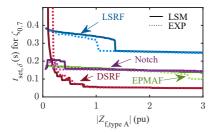

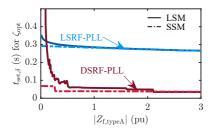

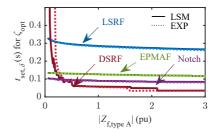

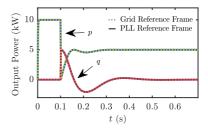

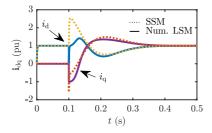

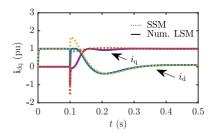

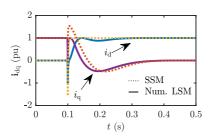

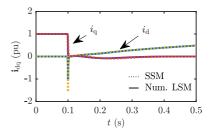

|   |     | 5.5.2 Dynamic Response on Type A Faults                                      | 91  |

|   | 5.6 | Impact of the PLL on the Voltage Oriented Control Considering Power Factor   |     |

|   |     | and Converter Current                                                        | 93  |

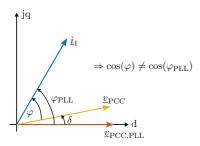

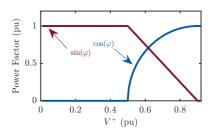

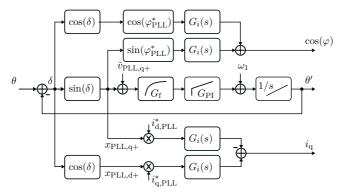

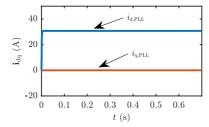

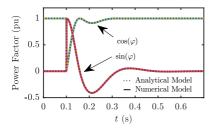

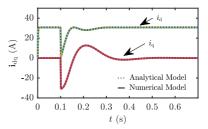

|   |     | 5.6.1 PLL Impact on the Converter Power Factor                               | 97  |

|   |     | 5.6.2 PLL Impact on the Converter Current Control                            | 98  |

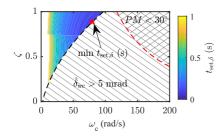

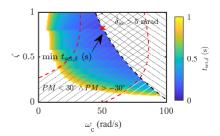

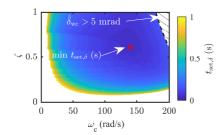

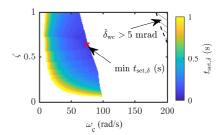

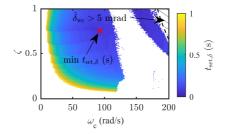

|   | 5.7 | Multi-Fidelity Model-based Design for PLLs under Severe Grid Disturbances    | 104 |

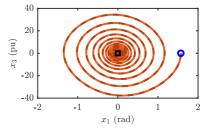

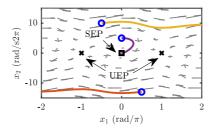

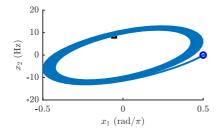

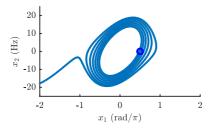

|   | 5.8 | Transient Stability Phenomena caused by the PLL                              | 107 |

| 6 | Gri | d-following Converter Control for Unbalanced Fault Ride-Through              |     |

|   | Ope | eration Considering Grid Strength                                            | 113 |

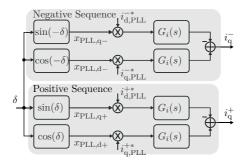

|   | 6.1 | Dual Sequence Current Control for Severe Unbalanced Grid Faults and Weak     |     |

|   |     | Grid Conditions                                                              | 115 |

|   |     | 6.1.1 Voltage Limitation Schemes                                             | 119 |

|   |     | 6.1.2 Evaluation and Modeling of the Dual Sequence Current Control during    |     |

|   |     | Severe Voltage Sags and Phase Jumps                                          | 122 |

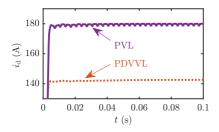

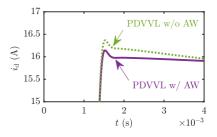

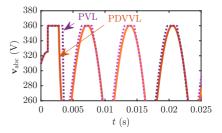

|   |     | 6.1.3 Experimental Validation of Dual Sequence PR-controllers with Voltage   |     |

|   |     | Limitation and Anti-Windup                                                   | 125 |

|    | 6.2 Impact of Unbalanced Grid Faults on Grid Converters: Model and A<br>DC-link Oscillations |                                                                                                                                                                                                                                                                                                                                                                              | 127                                           |

|----|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

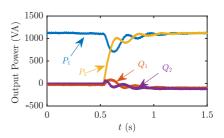

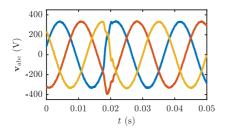

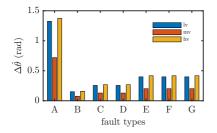

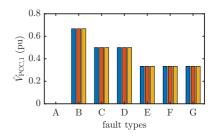

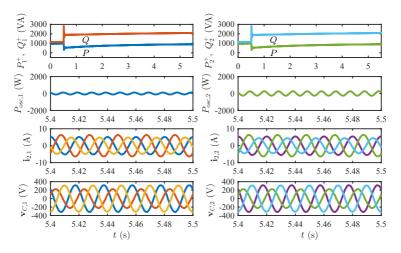

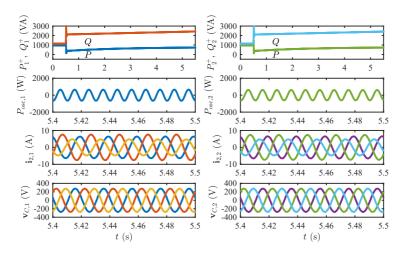

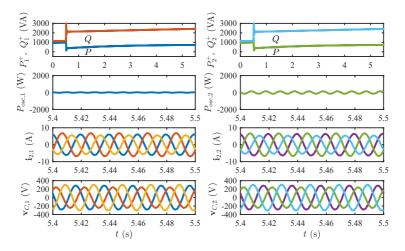

|    | 6.3                                                                                          | <ul> <li>Dual Sequence Current Reference Calculation Schemes, Voltage Support Schemes, and the Grid Codes</li> <li>6.3.1 Rejection of Power Oscillations Considering the Current Limitation</li> <li>6.3.2 Validation of the Control Characteristics and DC-Link Oscillations</li> <li>6.3.3 Grid support based on Voltage Support Scheme (VSS) and VDE-AR-N 4110</li> </ul> | 131<br>133<br>137<br>139                      |

|    | 6.4                                                                                          | Evaluation of Dual Sequence Power Reference Schemes during Fault Ride-                                                                                                                                                                                                                                                                                                       |                                               |

|    | 6.5                                                                                          | <ul> <li>Through</li></ul>                                                                                                                                                                                                                                                                                                                                                   | 141<br>144<br>144<br>146                      |

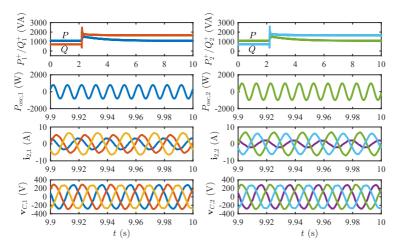

| 7  | <b>Gri</b><br>7.1<br>7.2                                                                     | d-forming Converter Control for Fault Ride-Through in Weak Grids<br>Design of Positive Sequence Droop-Control with Virtual Impedance<br>Droop Control for Unbalanced Operation Scenarios Considering Fault Ride-<br>Through                                                                                                                                                  | 140<br>153<br>154<br>157                      |

| 8  | Con                                                                                          | uclusion and Outlook                                                                                                                                                                                                                                                                                                                                                         | 165                                           |

| Bi | bliog                                                                                        | graphy                                                                                                                                                                                                                                                                                                                                                                       | 169                                           |

| Pι | ıblica                                                                                       | ations                                                                                                                                                                                                                                                                                                                                                                       | 182                                           |

| Fi | gure                                                                                         | S                                                                                                                                                                                                                                                                                                                                                                            | 185                                           |

| Ta | bles                                                                                         |                                                                                                                                                                                                                                                                                                                                                                              | 194                                           |

| A  | A.2<br>A.3<br>A.4                                                                            | Converter Losses                                                                                                                                                                                                                                                                                                                                                             | <b>197</b><br>197<br>197<br>199<br>201<br>202 |

| в  | Lya                                                                                          | punov Function for SRF-PLLs in Weak Grids                                                                                                                                                                                                                                                                                                                                    | 205                                           |

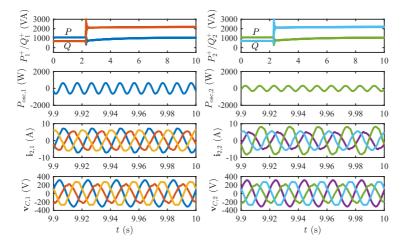

| С  | Pow                                                                                          | ver References for Grid-forming Converters                                                                                                                                                                                                                                                                                                                                   | 207                                           |

| AARC           | Average Active–Reactive Control, 131, 136 f., 141 f., 158 f., 166,                                  |

|----------------|-----------------------------------------------------------------------------------------------------|

|                | 207                                                                                                 |

| ADC            | Analog-Digital-Converter, 53, 87                                                                    |

| ANS            | Amplitude Normalization Scheme, 59 f., 65, 79, 81, 95, 103                                          |

| BPSC           | Balanced Positive Sequence Control, 131, 136 f., 141, 158                                           |

| CPU            | Central Processing Unit, 40, 47, 53 f., 87                                                          |

| DI             | Digital Input, 53                                                                                   |

| DO             | Digital Output, 53                                                                                  |

| DSOGI          | Dual-Second-Order-Generalized Integrator, 10, 57, 71 f., 74, 80,                                    |

|                | 85, 103, 105 f., 112 f., 115, 118, 122, 124, 135, 153, 165                                          |

| DSRF           | Dual Synchronous Reference Frame, 10, 33, 57 f., 68–74, 80, 82,                                     |

|                | 85, 88, 90 ff., 99, 103, 105 ff., 165                                                               |

| EAC            | Equal Area Criterion, 107, 145, 148, 151                                                            |

| EMI            | Electromagnetic Interference, 40, 47 f.                                                             |

| EPMAF          | Enhanced Moving Average Filter with Prefiltering Stage, 74 f.,                                      |

|                | 80 ff., 85, 92, 99, 105                                                                             |

| EXP            | Experiment, 90                                                                                      |

| FFT            | Fast Fourier Transformation, 28, 137                                                                |

| FOH            | First-Order-Hold, 54                                                                                |

| FPGA           | Free Programmable Gate Array, 40, 47, 53 ff., 87                                                    |

| FPNSC          | Flexible Positive and Negative Sequence Control, 131 f., 141                                        |

| FRT            | Fault Ride-Through, 6, 24 f., 29 ff., 39, 42, 50, 63, 67, 97, 113 f.,                               |

|                | 118, 127, 140, 153, 156                                                                             |

| GUI            | General User Interface, 47                                                                          |

| HVRT           | High-Voltage Ride-Through, 8, 29                                                                    |

| IARC           | Instantaneous Active–Reactive Control, 131                                                          |

| IGBT           | Insulated Gate Bipolar Transistor, $5, 16, 42, 47 f., 50, 52, 124$ ,                                |

|                | 197                                                                                                 |

| ISC            | Instantaneous Symmetrical Components, 19 f., 23, 198                                                |

| LOS            | Loss of Synchronization, 6, 107, 145, 148, 150 f.                                                   |

| $\mathbf{LPF}$ | Low-Pass Filter, 153, 159                                                                           |

| $\mathbf{LSM}$ | $ {\rm Large-Signal\ Model,\ 10,\ 40\ ff.,\ 58,\ 60\ f.,\ 71\ f.,\ 74,\ 76,\ 87,\ 90\ ff.,\ 95, } $ |

|                | 99, 101, 103, 105 f., 113, 124, 137                                                                 |

| LSRF            | Synchronous Reference Frame with Low-Pass Filters, 58, 60 ff., 67, 69 f., 74, 77–80, 82, 85, 92, 95, 99, 101, 105, 107, 109 ff., 165 |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------|

| LTI             | Linear Time-Invariant, 42, 69, 72, 107, 144 f., 166                                                                                  |

| LTP             | Linear Time-Invariant, 42, 69, 72, 107, 1441., 100<br>Linear Time-Periodic, 72, 166                                                  |

|                 |                                                                                                                                      |

| LVRT            | Low-voltage Ride-Through, 8, 29                                                                                                      |

| MAF             | Moving Average Filter, 57, 73 ff.<br>Matal arrida comison ductor field affect transiston 47, 52                                      |

| MOSFET          | Metal-oxide-semiconductor field-effect transistor, 47, 52                                                                            |

| MPPT            | Maximum Power Point Tracking, 8, 32                                                                                                  |

| MRF<br>Nf       | Multiple Reference Frame, 72                                                                                                         |

| ODE             | Notch-filter, 57, 73–76, 79 f., 82, 85 f., 92, 99, 101, 103, 105                                                                     |

|                 | Ordinary Differential Equation, 42 f., 145, 148                                                                                      |

| P               | Proportional, 32<br>Drinted Circuit Record 48, 50                                                                                    |

| PCB             | Printed Circuit Board, 48, 50<br>Point of Common Counting 2, 12 f 25 f 20 f 22, 47, 57, 101                                          |

| PCC             | Point of Common Coupling, 3, 13 f., 25 f., 29 f., 32, 47, 57, 101, 114, 144 f., 154 f., 157, 159, 162                                |

| $\mathbf{PCL}$  | Peak Current Limitation, 36                                                                                                          |

| PDVVL           | Peak and Delayed Vector Voltage Limitation, 119, 135                                                                                 |

| $\mathbf{PHIL}$ | Power Hardware in the Loop, $166$                                                                                                    |

| PI              | Proportional-Integral, 32 ff., 37, 57, 59, 62, 80, 113, 115–119, 145, 148                                                            |

| PLL             | Phase-Locked Loop, VII ff., 6, 9 f., 28, 32 f., 41 f., 52–55, 57–63,                                                                 |

| 1 11            | $65-99,\ 101,\ 103,\ 105\mathrm{ff.},\ 109-115,\ 122,\ 124,\ 144\mathrm{ff.},\ 148,\ 150\mathrm{ff.},$                               |

|                 | 165 f., 199 f., 205 f.                                                                                                               |

| PNSC            | Positive- and Negative-Sequence Control, $131,136\mathrm{f.},141\mathrm{f.},158$                                                     |

| $\mathbf{PR}$   | Proportional-Resonant, 32 ff., 38, 55, 113–119, 124, 135, 144 f., 202 f.                                                             |

| $\mathbf{PS}$   | Power Supply, 47, 137                                                                                                                |

| PSC             | Positive Sequence Calculator, 71                                                                                                     |

| PT1             | First Order Lag Element, 93, 113, 116 ff.                                                                                            |

| $\mathbf{PV}$   | Photovoltaic, 1, 3, 6, 13, 16, 32, 50                                                                                                |

| $\mathbf{PVL}$  | Peak Voltage Limitation, 113, 119                                                                                                    |

| $\mathbf{PWM}$  | Pulse-Width Modulation, 16                                                                                                           |

| RCP             | Rapid Control Prototyping, 40, 46 f., 49, 51, 53, 55, 87 ff., 91, 137                                                                |

| RES             | Renewable Energy Sources, 1, 3, 5 f., 8, 13 f., 16, 24 f., 29, 31, 40,                                                               |

|                 | 43, 48, 67                                                                                                                           |

| $\mathbf{RMS}$  | Root-Mean-Square, 28 f., 141                                                                                                         |

| ROA             | Region of Attraction, 10, 114, 145, 149 ff., 165                                                                                     |

| ROCOF           | Rate of Change of Frequency, $15$                                                                                                    |

| SCR             | Short Circuit Ratio, 14, 24, 46, 114, 131, 141–145, 148 ff., 153 ff.,                                                                |

|                 | 157, 159, 162 f., 165 f.                                                                                                             |

| SEP             | Stable Equilibrium Point, 41, 107, 148 ff.                                                                                           |

| $\mathbf{SiC}$  | Silicon Carbide, 47, 52, 87, 89, 91                                                                                                  |

| SO              | Symmetrical Optimum, 10, 57 f., 76, 78–82, 107, 110 f., 154, 199                                                                     |

|                 |                                                                                                                                      |

| SOGI<br>SPWM<br>SRF<br>SSM | Second Order Generalized Integrator, 68, 71 f.<br>Sinusoidal Pulse-Width Modulation, 16, 87, 115, 117, 197, 202<br>Synchronous Reference Frame, 22 f., 33 f., 57 ff., 69, 71, 75, 79, 88,<br>97, 107, 145, 148, 205 f.<br>Small-Signal Model, 10, 42, 58, 60 f., 65, 69, 71 f., 74–77, 80, 82, |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5511                       | 84 f., 87, 90, 92, 97, 99, 103, 105, 113, 118, 124                                                                                                                                                                                                                                             |

| STATCOM                    | Static Synchronous Compensator, 6                                                                                                                                                                                                                                                              |

| $\mathbf{SVM}$             | Space Vector Modulation, 16                                                                                                                                                                                                                                                                    |

| $\operatorname{THD}$       | Total Harmonic Distortion, 113, 142                                                                                                                                                                                                                                                            |

| UEP                        | Unstable Equilibrium Point, 41, 107, 148 f.                                                                                                                                                                                                                                                    |

| VCL                        | Vector Current Limitation, 36, 132                                                                                                                                                                                                                                                             |

| VOC                        | Voltage Oriented Control, 10, 32 ff., 36, 46, 52 f., 57, 93 ff., 97, 99, 101, 103, 113 ff., 119, 122, 145, 153, 165 f.                                                                                                                                                                         |

| VSC                        | Voltage Source Converter, 6, 16, 48, 57                                                                                                                                                                                                                                                        |

| VSG                        | Virtual Synchronous Generator, 32                                                                                                                                                                                                                                                              |

| $\mathbf{VSS}$             | Voltage Support Scheme, 131 f., 138, 141, 143, 159, 165 f., 207                                                                                                                                                                                                                                |

| $\mathbf{VVL}$             | Vector Voltage Limitation, 113, 119, 135                                                                                                                                                                                                                                                       |

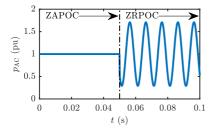

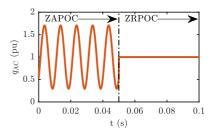

| ZAPOC                      | Zero Active Power Oscillation Control, 133 f., 136 ff., 141 ff., 165                                                                                                                                                                                                                           |

| ZOH                        | Zero-Order-Hold, 54 f.                                                                                                                                                                                                                                                                         |

| ZRPOC                      | Zero Reactive Power Oscillation Control, $133{\rm f.},136{\rm f.},141{\rm f.}$                                                                                                                                                                                                                 |

## Nomenclature

| fs                                              | Sampling frequency, 54                                                       |

|-------------------------------------------------|------------------------------------------------------------------------------|

| Js<br>fsw                                       | Converter switching frequency, 43, 48, 50                                    |

| Jsw<br>f <sub>res</sub>                         | Filter resonance frequency, 48                                               |

| J res<br>D                                      | Feedthrough matrix, 44                                                       |

| C<br>C                                          | Output matrix, 44                                                            |

| В                                               | Input matrix, 44                                                             |

| A                                               | State or system matrix, 44                                                   |

| у                                               | Output vector, 43 f.                                                         |

| y<br>X                                          | State vector, 43                                                             |

| u                                               | Input vector, 43 f.                                                          |

| $\cos(\varphi)$                                 | Power factor, 5                                                              |

| m                                               | Modulation index defined as fundamental frequency amplitude                  |

| 110                                             | to $V_{\rm dc}/2$ ratio, 5                                                   |

| VUF                                             | Ratio of negative sequence voltage to positive sequence voltage              |

| 101                                             | (voltage unbalance factor), 26, 29, 65, 67, 71, 136 f., 157, 159             |

| $\underline{D}$                                 | Complex voltage characteristic factor, 26                                    |

| $\frac{Z}{T}$                                   | Period of a time-periodic oscillation, 22                                    |

| $\mathbf{T}_{\mathrm{dq}^n}$                    | Park transformation matrix locked on the $n$ -th harmonic, 23                |

| $\mathbf{T}_{dq^{-1}}$                          | Park transformation matrix for the negative sequence, 24                     |

| $\mathbf{T}_{\mathrm{dq}}$                      | Park transformation matrix, 22 f., 33, 59                                    |

| $\mathbf{x}_{\mathrm{dq}}^{n}$                  | Vector of the $n$ -th harmonic of the three-phase system in $dq$ -frame,     |

| uq                                              | 23                                                                           |

| $\mathbf{x}_{da}^{-}$                           | Negative sequence vector of a three-phase system in $dq$ -frame, 23          |

| $f{x}_{dq}^- \ f{x}_{dq}^+$                     | Positive sequence vector of a three-phase system in $dq$ -frame, 23          |

| $\mathbf{x}_{\mathrm{dq}}$                      | Vector of a three-phase system in $dq$ -frame, 23                            |

| $\mathbf{x}_{\alpha\beta}^{-}$                  | Negative sequence vector of a three-phase system in $\alpha\beta$ -frame, 22 |

| $\mathbf{x}^{lphaeta} \ \mathbf{x}^+_{lphaeta}$ | Positive sequence vector of a three-phase system in $\alpha\beta$ -frame, 22 |

| $\mathbf{T}_{\alpha\beta0}$                     | Real Clarke transformation matrix, 21                                        |

| $\underline{\mathbf{T}}_{\alpha\beta}$          | Complex Clarke transformation matrix, 21                                     |

| $x_0$                                           | Complex common mode component of an arbitrary three-phase                    |

|                                                 | system, 20 f.                                                                |

| $x_{\beta}$                                     | Complex $\beta$ component of an arbitrary three-phase system in              |

|                                                 | $\alpha\beta$ -frame, 20 ff.                                                 |

|                                                 |                                                                              |

| $x_{\alpha}$                                | Complex $\alpha$ component of an arbitrary three-phase system in $\alpha^{\beta}$ frame 20 ff             |

|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| $\underline{\mathbf{T}}_{0}$                | $\alpha\beta$ -frame, 20 ff.<br>Transformation matrix for the zero sequence in the <i>abc</i> -frame, 19, |

| _                                           | 197                                                                                                       |

| $\underline{\mathbf{T}}_{-}$                | Transformation matrix for the negative sequence in the <i>abc</i> -frame, 19, 21, 197                     |

| $\underline{\mathbf{T}}_+$                  | Transformation matrix for the positive sequence in the <i>abc</i> -frame, $10, 21$                        |

| $\underline{\mathbf{T}}_{+-0}$              | 19, 21<br>Transformation matrix for the positive/negative/zero sequence                                   |

| <u> </u>                                    | for phase a in the <i>abc</i> -frame, 19                                                                  |

| $\underline{q}$                             | Simplified complex transformation constant for Clark Transfor-                                            |

| 1                                           | mation representing a 90° phase lag or $T/2$ phase shift, 19–22                                           |

| <u>a</u>                                    | Complex transformation constant for Clark Transformation, 18 f.,                                          |

| _                                           | 21                                                                                                        |

| $\vec{\mathbf{x}}_{\mathrm{abc}}$           | Arbritrary phasor vector of three-phase quantities of phase a/ b/                                         |

| abe                                         | c in the positive/ negative/ zero sequence, 19, 21                                                        |

| $\mathbf{x}_{\mathrm{abc}}$                 | Arbritrary time-domain vector of three-phase quantities of phase                                          |

|                                             | a/b/c in the positive/ negative/ zero sequence, 20 f.                                                     |

| $ec{\mathbf{x}}_{\mathrm{a}}^{+-0}$         | Arbritrary phasor vector of three-phase quantities of phase a in                                          |

| u                                           | the positive/ negative/ zero sequence, 18 f.                                                              |

| $\underline{\mathbf{x}}_{\mathrm{a}}^{+-0}$ | Arbritrary complex vector of three-phase quantities of phase a in                                         |

| u                                           | the positive/ negative/ zero sequence, 18                                                                 |

| $\theta$                                    | Phase angle of the positive sequence grid voltage, 13, 22                                                 |

| $f_n$                                       | Instantaneous frequency of the <i>n</i> -th harmonic of the grid voltages,                                |

|                                             | 13                                                                                                        |

| $\omega_1$                                  | Instantaneous fundamental angular frequency of the grid voltages,                                         |

|                                             | 13, 22, 33, 154                                                                                           |

| $f_1$                                       | Instantaneous fundamental frequency of the grid voltages, 13, 15                                          |

| $S_{\rm sc}$                                | Apparent Power of the grid source during a Short-Circuit of the                                           |

|                                             | Point of Common Coupling, 14                                                                              |

| $\mathbf{v}_{\mathrm{conv}}^{*}$            | Vector of instantaneous converter reference voltages, $33$                                                |

| $\mathbf{v}_{\mathrm{S}}$                   | Vector of instantaneous grid (source) voltages, 3, 43, 45                                                 |

| $\mathbf{v}_{\mathrm{conv}}$                | Vector of instantaneous converter voltages, 43, 45                                                        |

| $v_{\rm c,PCC}$                             | Instantaneous PCC voltage of phase c, $25$                                                                |

| $v_{\rm b,PCC}$                             | Instantaneous PCC voltage of phase b, $25$                                                                |

| $v_{\rm a,PCC}$                             | Instantaneous PCC voltage of phase a, $25$                                                                |

| $v_{\rm c}$                                 | Instantaneous grid voltage of phase c, $13$                                                               |

| $v_{\rm b}$                                 | Instantaneous grid voltage of phase b, 13                                                                 |

| $v_{\rm a}$                                 | Instantaneous grid voltage of phase a, 13                                                                 |

| $\hat{V}_{\mathrm{S},n}$                    | Magnitude of the $n$ -th harmonic of the grid voltage, 13                                                 |

| $\hat{V}_{ m S}$                            | Magnitude of the grid voltage. Commonly called source voltage, 13, 33                                     |

| $\mathbf{v}_{\mathrm{PCC}}$                 | Vector of PCC phase voltages (abc), 33, 47                                                                |

| $\mathbf{v}_{C}$               | Vector of capacitor phase voltages (abc), 33, 43, 47, 50, 53, 153    |

|--------------------------------|----------------------------------------------------------------------|

| $\mathbf{i}_2$                 | Vector of grid side phase currents (abc), 43, 45, 47, 153            |

| $\mathbf{i}_1$                 | Vector of converter side phase currents (abc), 33, 43, 47, 115, 118, |

|                                | 122                                                                  |

| $C_{\rm f}$                    | Filter capacitance, 50                                               |

| $L_{2f}$                       | Grid side filter inductor, 48, 145, 154                              |

| $L_{1f}$                       | Converter side filter inductor, 50, 93, 116 f., 119                  |

| $R_{L2f}$                      | Parasitic resistance of the grid side filter inductance, 45, 145     |

| $R_{L1f}$                      | Parasitic resistance of the converter side filter inductance, 45,    |

|                                | 116 f.                                                               |

| $R_{\rm S}$                    | Resistive part of the source impedance of the grid bus to the        |

|                                | Point of Common Coupling, 15, 46                                     |

| $L_{\rm S}$                    | Inductive part of the source impedance of the grid bus to the        |

|                                | Point of Common Coupling, 15, 46                                     |

| $C_{\rm S}$                    | Capacitive part of the source impedance of the grid bus to the       |

|                                | Point of Common Coupling, 15                                         |

| $i_{\mathrm{dc},n}$            | dc-Link current of the $n$ th-converter or the generator current of  |

|                                | the <i>n</i> th-renewable energy source, $\frac{3}{2}$               |

| $i_{\rm dc}$                   | dc-Link current of the converter or the generator current of the     |

|                                | renewable energy source, 3, 137                                      |

| $V_{\rm dc}$                   | dc-Link voltage of the converter, $5, 33, 47, 50, 119, 130$          |

| $\underline{Z}_{\mathrm{L},n}$ | Line impedance of the $n$ th-converter bus to the Point of Common    |

|                                | Coupling, 3                                                          |

| $\underline{Z}_{\mathrm{F}}$   | Fault impedance of the fault bus to the Point of Common Cou-         |

|                                | pling, 3, 25 ff., 66, 71, 74, 84, 103, 122, 134, 157, 159            |

| $\underline{Z}_{\mathrm{L}}$   | Line impedance of the converter bus to the Point of Common           |

|                                | Coupling, 3, 154 f.                                                  |

| $\underline{Z}_{S}$            | Source impedance of the grid bus to the Point of Common Cou-         |

|                                | pling, 3, 14, 25 ff., 43, 66, 84, 103, 148, 154                      |

## Introduction

Increasing electrification in most areas of life leads to more process efficiency and comfort, and thus prosperity for all people. Especially, efforts in automotive electro-mobility, electric aircraft, and industrial automation will enable higher mobility, less pollution, and increasing sustainability. Prosperity often leads to increased energy consumption that seems to be in contrast with sustainability. However, this is not always true and consuming more electrical power could be sustainable, if the power is generated by Renewable Energy Sources (RES). This sustainable power consumption requires high efforts in efficient power generation, conversion, and transportation. Solving and improving these key elements will pave the way to reliably, robustly, and sustainably generated and distributed power, and thus lasting prosperity by electrifying most areas of life.

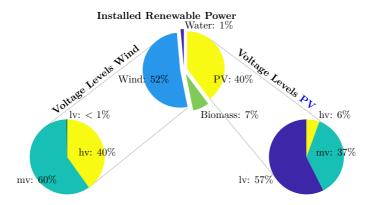

RES with their power electronic front ends are the backbone of sustainable electrification. Already 46% of the electric energy is generated by RES in Germany [1]. Particularly, wind power and Photovoltaic (PV)-generators rely on power electronic front ends that start to affect power system operation and stability. Hence, the power electronic dominated grid is a plausible future scenario and already real in some grid parts with a large share of RES. The problem with fluctuating power of RES attracts much attention in recent research. Proposed solutions, such as increasing energy storage integration or transportation capacity, are discussed by a broad research community and are followed by a large public. However, present and future power systems are also adversely affected by less obvious phenomena that are closely related to power electronic components, their control, and their interaction with other power system components.

A spectacular power system disruption caused by power converters happened in 2016 in California. Due to the tripping of several transmission lines during a fire, 1.2 GW PV generation also tripped that caused power outage in a large area [2]. Surprisingly, it was not the decreased transmission capacity of the power system that induced the interruption, but a special instability phenomenon of PV converters. This example highlights the importance of the fast-evolving research field of grid converters. Understanding these power electronic components and their interactions with power systems is crucial to safely operate present and

future power systems. Consequently, this thesis focuses on developing models and analysis methods to understand these interactions, deriving design processes and enhancing existing controls to improve the control performance of grid converters.

# 2

## Critical Converter Properties Concerning Weak Grids and Fault Ride-Through

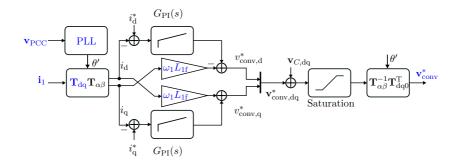

Shifting our electricity generation towards PV and wind power leads to a tremendously increasing number of power electronic converters in the power systems. Two essential properties dominate how converters interact with the grid: first, converter characteristics are predominantly affected by their control; second, their maximum output current is very limited compared to conventional synchronous generators. Converter control is getting more complex and diverse to sufficiently handle most of the occurring grid scenarios. Two basic control concepts are the grid-following and grid-forming control, where the grid-following concept controls the output current of the converter and the grid-forming concept controls the output voltage. Particularly, adverse grid conditions, such as unbalanced grid faults, may critically affect stability and performance of these controls. Unbalanced faults cause voltage magnitudes and angles to differ from the normal operation and demand complex control structures and sophisticated modeling of the converter. The small maximum output current of converters leads to weak grid parts, where the grid voltages are prone to disturbances and sensitive to power variations. Weak grid parts are vulnerable to new instability mechanisms and power quality problems. Consequently, this thesis focuses on the modeling, analysis, and control of grid converters in weak electric grids and during unbalanced grid faults.

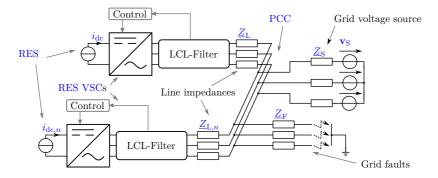

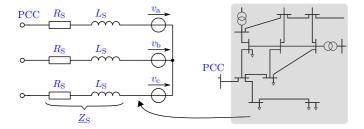

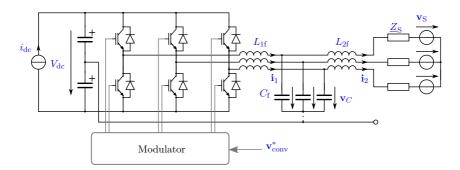

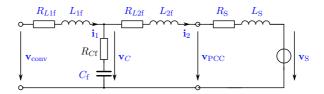

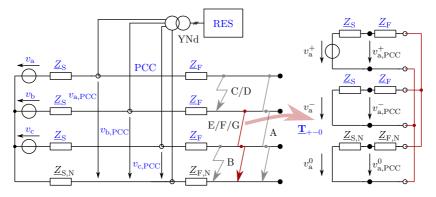

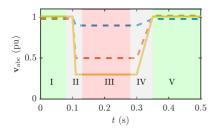

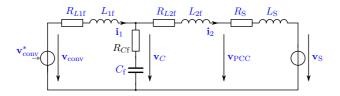

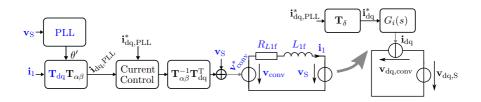

A suitable system topology is the starting point of the analysis. Here, a trade-off between system complexity and sufficiently representing the original system behavior must be considered. The chosen topology contains at least two RES-converters fed by a current source with  $i_{dc}$  ( $i_{dc,n}$ ) and connected to a Point of Common Coupling (PCC), as shown in Fig. 2.1. The PCC connects several converters to the grid through a line impedance  $Z_{L}$  ( $Z_{L,n}$ ). The grid is modeled by a voltage source  $\mathbf{v}_{S}$  and source impedance  $Z_{S}$ , which can be used to emulate weak grids by increasing  $Z_{S}$ , as presented in section 3.1.1. The fault models include different types of short-circuits and varying fault impedances  $Z_{F}$  according to section 3.3. This small multi-converter system can be used to investigate parallel converter scenarios without extensive complexity. Based on this topology, the critical converter characteristics in weak and unbalanced grid scenarios are described throughout this chapter.

Converter characteristics during faults are part of several standards (see section 3.3). However, these standards do not address limits of converter hardware and control, and they typically

Figure 2.1: Multi-converter setup with line impedance  $(\underline{Z}_{L}, \underline{Z}_{L,n})$ , grid and fault model.

do not consider different grid scenarios such as fault types and line impedances. Requirements based on a single grid scenario simplify the control design, but do not necessarily achieve the desired support of the grid voltage. An example of this is the requirement to inject reactive power during voltage sags. The standards recommend that the converters should inject reactive power to recover the voltage at the PCC, but injecting reactive and active power depending on the line impedance ratio achieves much better voltage recovery [3, pp.116-119]. This example highlights that the grid codes must be extended, and further investigations on converter hardware and control are crucial for operating converter dominated grids safely and reliably. Therefore, the following investigations are categorized into: safe converter operation, optimized converter utilization, and optimized grid support. Safe converter operation prevents converter tripping and is crucial for the converter to continue injecting power and supporting the grid voltage. Optimized utilization mainly focuses on optimizing converter operation regarding aging of components or efficiency. In contrast, the optimized grid support mainly addresses how the converter can support the grid voltages.

## 2.1 Safe Converter Operation

Safe converter operation requires that converter currents and voltages are limited. The maximum current is closely related to the thermal limits of semiconductors, whereas the voltage limits primarily depend on their maximum blocking voltages. Exceeding these values may damage the semiconductors or trip fuses. Although state-of-the-art converter control typically limits the converter currents and voltages, the control may be unstable during critical operational scenarios, which may also trip the converter.

The maximum converter rating and a stable control are crucial for safe grid operation. The converter rating mainly depends on losses and the thermal limits of the converter. Hence,

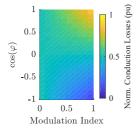

Figure 2.2: IGBT conduction losses dependent on m and  $\cos(\varphi)$ .

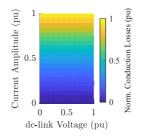

Figure 2.3: Overall conduction losses dependent on  $V_{\rm dc}$  and  $\hat{I}$ .

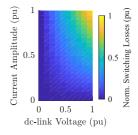

Figure 2.4: Characteristics of IGBT switching losses dependent on  $V_{\rm dc}$  and  $\hat{I}$ .

semiconductor losses are discussed to assess thermal limits without considering the details of the converter cooling system and mechanical design. Some practical details on converter design are provided in chapter 4. Control stability predominantly depends on the control structure and operational scenarios. Consequently, two critical instability phenomena are introduced at the end of this section.

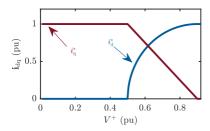

Especially during grid faults, converters may need to provide maximum current, and the broad operation range of the modulation index m, power factor  $\cos(\varphi)$ , and current make fault scenarios even more critical. From the converter's point of view and considering only electrical parameters, particularly m,  $\cos(\varphi)$ , the dc-link voltage  $V_{\rm dc}$ , and the maximum current affect the converter losses. These losses include conduction losses and switching losses of the typically applied Insulated Gate Bipolar Transistors (IGBTs) and diodes. The overall conduction losses may not change significantly with m and  $\cos(\varphi)$ , but the loss distribution between diodes and IGBTs is changing [4], [5, pp.277-279]. Conduction losses predominantly depend on the current magnitude if the collector-emitter threshold voltage of the IGBT is similar to the forward threshold voltage of the diode and the on-state resistance of the IGBT is similar to the on-state resistance of the diode, as shown in Fig. 2.2 and 2.3. A proof for this characteristic is given in appendix A.1. The switching losses of the converter do not depend on m and  $\cos(\varphi)$  but change with  $V_{\rm dc}$  and the current amplitude as presented in Fig. 2.4 [4], [5]. In most RES converters, the dc-link voltage is kept near a constant reference, and thus only the maximum current significantly affects the losses and defines the thermal limits of the converter.

The specification of the maximum current is mainly restricted by costs and efficiency. However, designing converters for higher current rating becomes necessary for supporting the grid voltages. For grid-following converters, typical current ratings vary in the range of 1-2 pu of the rated current [3], [6], [7]. Grid-forming converters have current ratings up to 3-5 pu [3], [7]. Particularly in weak grids, the converter rating significantly affects the grid voltages and must be selected thoroughly, which is discussed in chapter 7.

Chapter 2. Critical Converter Properties Concerning Weak Grids and Fault Ride-Through

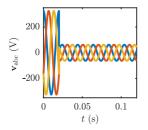

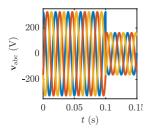

Figure 2.5: Fault voltages during a balanced three-phase fault in the low voltage grid.

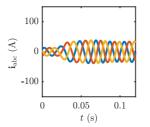

Figure 2.6: Converter currents during a balanced three-phase fault with a stable response.

Figure 2.7: Converter currents during a balanced three-phase fault with an unstable response.

Current limitation concepts significantly alter steady-state characteristics, control dynamics, and thus stability. Since the limitation methods depend on the current control, the necessary background and analysis on these controller components is presented in chapter 5. Then, detailed investigations on their impact on the control under unbalanced grid faults are presented in chapter 6 and chapter 7. These chapters answer two main questions:

- 1. How to limit the converter current during severe, unbalanced grid faults?

- 2. How to design a limitation with minimum effect on the power control or grid support functionality?

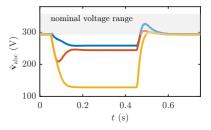

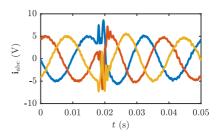

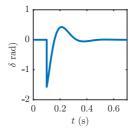

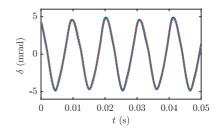

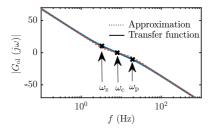

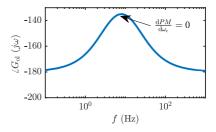

Converter tripping may occur due to limitation failure or unstable converter control. Notably, severe grid faults are critical for control stability due to severe grid voltage transients. For example, in Fig. 2.5 a three-phase fault may result in grid voltage waveforms that contain a severe magnitude step and grid angle jump. During these severe grid voltage transients, two stability related mechanisms are the Loss of Synchronization (LOS) [8], [9] and controller latch-up [10]. The LOS is predominantly caused by the PLL and its interaction with the current control under weak grid conditions. Exemplary, Fig. 2.6 and 2.7 show the phase currents for a stable and unstable PLL design, respectively. In the unstable case, converters may trip due to overcurrent, which leads to failing of the Fault Ride-Through (FRT) requirements. Unlike LOS, the latch-up is critical for cascaded control structures that are often used for grid-forming converters. However, the two instability mechanisms have one thing in common: the involved controller parts are nonlinear, since PLLs contain trigonometric terms and limitations often consist of magnitude calculations and saturation blocks. Following this, two main questions concerning stability are answered in chapters 5 and 6:

- 3. Which models can be used to describe these instability mechanisms, and does an analytical stability requirement exist?

- 4. How to design and evaluate the critical controller parts to achieve a stable and fast converter current step response during grid faults?

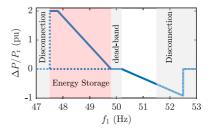

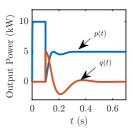

## 2.2 Optimized Converter Utilization

As discussed before, RES-Voltage Source Converters (VSCs) must operate within safety limits at any time, and especially during faults. But what is the optimum converter operating point during grid faults? From the converter's point of view, the faults demand high currents that must comply with the standards [11], [12], [13]. Additionally, unbalanced grid faults lead to unbalanced power in the three converter phases causing double fundamental frequency power oscillations. These oscillations give rise to harmonics in the output power, degradation of the dc-link capacitors, and overvoltages [14], [15]. These phenomena are particularly critical for PV-systems, wind farms, or Static Synchronous Compensators (STATCOMs) [16], [17], [18]. The modified pq-theory can describe power in unbalanced multi-phase systems according to [19, pp.82-87]. This theory reveals that the instantaneous active power propagates to the dc-link of the converter and causes currents with double fundamental frequency. These currents will change the dc-link voltage depending on the dc-link capacitor design. Hence, fault scenarios, converter power setpoints, and the capacitor design affect dc-link voltage oscillation magnitudes, and thus their impact on the control characteristics.

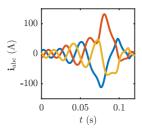

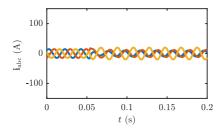

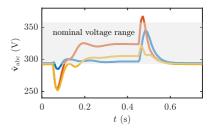

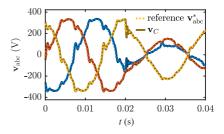

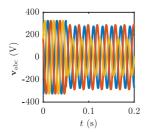

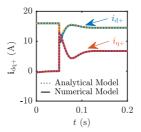

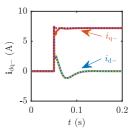

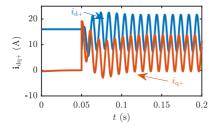

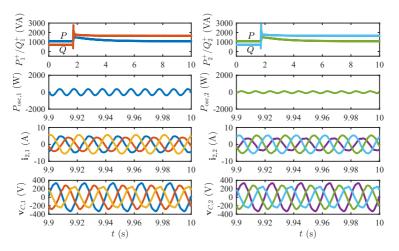

An exemplary simulation of a two-phase-to-ground fault demonstrates this behavior, and Fig. 2.8 shows the corresponding fault voltages and currents. In this test, the converter balances output currents, and the resulting instantaneous power oscillations cause dc-link voltage oscillations, as shown in Fig. 2.9. Since the grid voltages and converter currents determine these oscillations, they can be minimized by adequately choosing the converter current reference depending on the grid voltage.

Based on the presented characteristics, the following questions are of major interest and are discussed for the grid-following and grid-forming control in chapters 6 and 7, respectively:

- 5. How can dc-link voltage oscillations be described accurately by a generic model?

- 6. What influence does the dc-link capacitor design process have on the dc-link oscillations?

(b.4) = (b.2) = (b.2

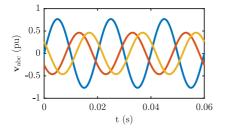

Figure 2.8: Grid voltages during a two-phase-toground fault.

7. How should the converter be controlled to limit dc-link voltage oscillations during unbalanced grid faults?

## 2.3 Grid Voltage Support

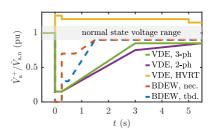

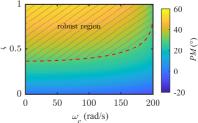

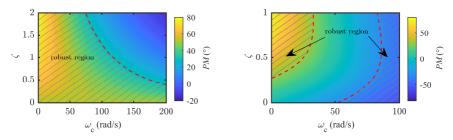

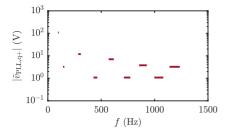

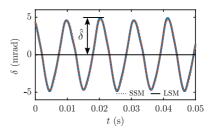

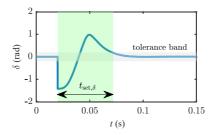

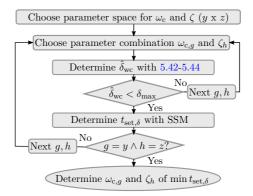

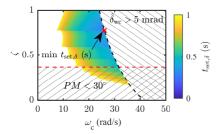

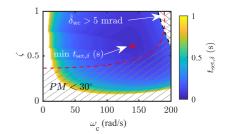

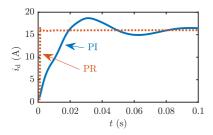

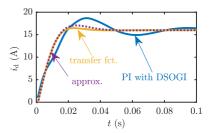

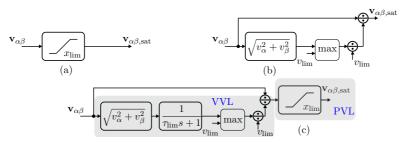

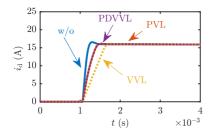

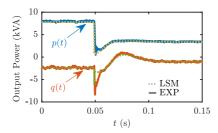

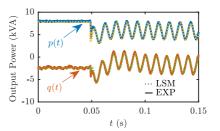

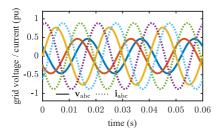

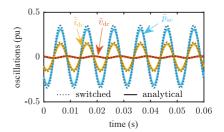

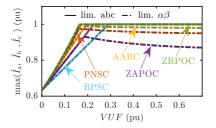

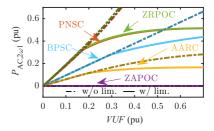

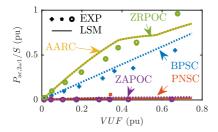

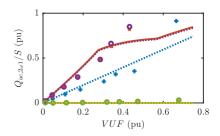

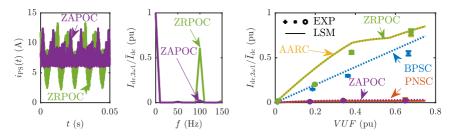

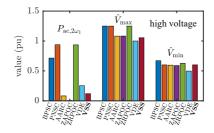

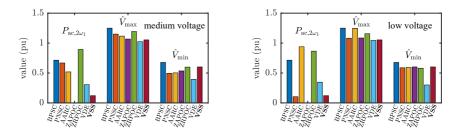

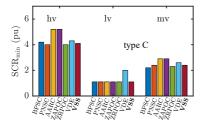

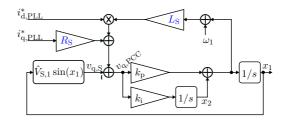

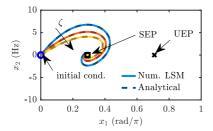

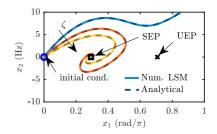

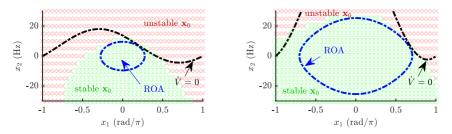

Nowadays, almost all RES converters must support the grid voltage and frequency. Operating RES with Maximum Power Point Tracking (MPPT) or maximum power injection without any grid support is not suitable for stable and reliable electric grid operation anymore due to the large share of RES. Injecting active and reactive power based on voltage and frequency deviations compared to their nominal values may keep voltages and frequencies in their predefined tolerance band. That means converters support the grid voltage and frequency during steady-state by injecting active and reactive power according to the standards [11], [12], [13]. During grid faults, generators should recover grid voltages into the normal state tolerance band, but this demands high currents depending on the grid strength. Complete voltage recovery is often not possible due to the low current rating of converters. At least, the grid voltages should stay in the Low-voltage Ride-Through (LVRT) and High-Voltage Ride-Through (HVRT) voltage tolerance band to prevent tripping of nearby loads or other RES [20].