Dhabaleswar K. Panda Michael Sullivan (Eds.)

# **Supercomputing Frontiers**

7th Asian Conference, SCFA 2022 Singapore, March 1–3, 2022 Proceedings

# Lecture Notes in Computer Science 13214

# Founding Editors

Gerhard Goos Karlsruhe Institute of Technology, Karlsruhe, Germany

Juris Hartmanis Cornell University, Ithaca, NY, USA

# **Editorial Board Members**

Elisa Bertino Purdue University, West Lafayette, IN, USA

Wen Gao Peking University, Beijing, China

Bernhard Steffen D TU Dortmund University, Dortmund, Germany

Moti Yung D Columbia University, New York, NY, USA More information about this series at https://link.springer.com/bookseries/558

Dhabaleswar K. Panda · Michael Sullivan (Eds.)

# Supercomputing Frontiers

7th Asian Conference, SCFA 2022 Singapore, March 1–3, 2022 Proceedings

*Editors* Dhabaleswar K. Panda Department of Computer Science and Engineering The Ohio State University Columbus, OH, USA

Michael Sullivan Material Science and Chemistry A\*STAR Institute of High Performance Computing Singapore, Singapore

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-031-10418-3 ISBN 978-3-031-10419-0 (eBook) https://doi.org/10.1007/978-3-031-10419-0

© The Editor(s) (if applicable) and The Author(s) 2022. This book is an open access publication.

**Open Access** This book is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this book are included in the book's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the book's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors, and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

# Preface

As the share of supercomputers in Asia continues to increase, the relevance of supercomputing merits a supercomputing conference for Asia. Supercomputing Asia 2022 (SCA22) was an umbrella of notable supercomputing events that promoted a vibrant HPC ecosystem in Asian countries.

The technical program of SCA22 provided a platform for leaders from both academia and industry to interact and to discuss visionary ideas, important global trends, and substantial innovations in supercomputing. Called the Supercomputing Frontiers Asia (SCFA) technical paper program, SCFA22, consisted of four tracks:

- Application, Algorithms, and Libraries

- Architecture, Network/Communications, and Management

- Data, Storage, and Visualization

- Programming and Systems Software

The submitted papers for the technical papers program went through a rigorous peer review process by an international program committee. A set of eight papers were finally selected for inclusion in the proceedings. The accepted papers cover a range of topics including HPC communication, GPU programming models, network service, large data set transfer, molecular dynamics simulation, and large-scale parallel applications. The quality of the papers is reflected in the proceedings that you find here. We would like to thank all authors for their submissions to this conference. Our sincere thanks to all Program Committee members for doing high-quality and in-depth reviewing of the submissions and selecting the papers for this year's program. We would like to thank the conference organizers for giving us the opportunity to serve this year's conference as the Co-Chairs for SCFA22.

April 2022

Dhabaleswar K. Panda Michael Sullivan

# Organization

# **Program Co-chairs**

| Dhabaleswar K. (DK) Panda | The Ohio State University, USA       |

|---------------------------|--------------------------------------|

| Michael Sullivan          | A*STAR Institute of High Performance |

|                           | Computing Singapore                  |

## **Program Committee**

Ritu Arora Olivier Aumage Ron Brightwell Rajkumar Buyya Maciej Cytowski Sandra Gesing

Mark Gray Bilel Hadri John Kim

Kishore Kothapalli

Bu Sung Lee Fang-Pang Lin

Jing Lou

Piotr Luszczek George S. Markomanolis **Ronald Minnich** Antonio J. Peña Depei Oian Martin Schulz Ryota Shioya Nathan Tallent Michela Taufer

Computing, Singapore

The University of Texas at San Antonio, USA Inria. France Sandia National Laboratories, USA The University of Melbourne, Australia Pawsey Supercomputing Centre, Australia University of Illinois Discovery Partners Institute, USA Pawsey Supercomputing Centre, Australia KAUST Supercomputing Lab, Saudi Arabia Korea Advanced Institute of Science and Technology, South Korea International Institute of Information Technology, Hyderabad, India Nanyang Technological University, Singapore National Center for High-Performance Computing, Taiwan A\*STAR Institute of High-Performance Computing, Singapore University of Tennessee Knoxville, USA CSC - IT Center for Science Ltd., Finland Sandia National Laboratory, USA Barcelona Supercomputing Center (BSC), Spain Beihang University Member, China Technical University of Munich, Germany The University of Tokyo, Japan Pacific Northwest National Laboratory, USA University of Tennessee, Knoxville, USA

Jingbo Wang Jianfeng Zhan

Joey Tianyi Zhou

The Australian National University, Australia Institute of Computing Technology, Chinese Academy of Sciences, China A\*STAR Institute of High Performance Computing, Singapore

# Contents

| High Performance Parallel LOBPCG Method for Large Hamiltonian        |     |

|----------------------------------------------------------------------|-----|

| Derived from Hubbard Model on Multi-GPU Systems                      | 1   |

| Susumu Yamada, Toshiyuki Imamura, and Masahiko Machida               |     |

| Vapor Condensation Under Electric Field: A Study Using Molecular     |     |

| Dynamics Simulation                                                  | 20  |

| Pengyu Wang and Zhong Chen                                           |     |

| The Effect of Wing Mass and Wing Elevation Motion During Insect      |     |

| Forward Flight                                                       | 31  |

| Jie Yao and K. S. Yeo                                                |     |

| Exploring the Dynamics of Quantum Information in Many-Body           |     |

| Localised Systems with High Performance Computing                    | 43  |

| Shao-Hen Chiew, Leong-Chuan Kwek, and Chee-Kong Lee                  |     |

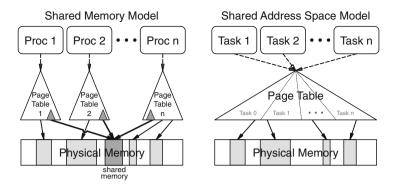

| On the Difference Between Shared Memory and Shared Address Space     |     |

| in HPC Communication                                                 | 59  |

| Atsushi Hori, Kaiming Ouyang, Balazs Gerofi, and Yutaka Ishikawa     |     |

| Evaluating GPU Programming Models for the LUMI Supercomputer         | 79  |

| George S. Markomanolis, Aksel Alpay, Jeffrey Young, Michael Klemm,   |     |

| Nicholas Malaya, Aniello Esposito, Jussi Heikonen, Sergei Bastrakov, |     |

| Alexander Debus, Thomas Kluge, Klaus Steiniger, Jan Stephan,         |     |

| Rene Widera, and Michael Bussmann                                    |     |

| Evaluating Methods of Transferring Large Datasets                    | 102 |

| Jakub Kopeć                                                          |     |

| Service Function Chaining Design & Implementation Using Network      |     |

| Service Mesh in Kubernetes                                           | 121 |

| Abdullah Bittar, Ziqiang Wang, Amir Aghasharif, Changcheng Huang,    |     |

| Gauravdeep Shami, Marc Lyonnais, and Rodney Wilson                   |     |

| Author Index                                                         | 141 |

# High Performance Parallel LOBPCG Method for Large Hamiltonian Derived from Hubbard Model on Multi-GPU Systems

Susumu Yamada<sup>1(⊠)</sup>, Toshiyuki Imamura<sup>2</sup>, and Masahiko Machida<sup>1</sup>

<sup>1</sup> Japan Atomic Energy Agency, Kashiwa, Chiba, Japan yamada.susumu@jaea.go.jp

<sup>2</sup> RIKEN, Kobe, Hyogo, Japan

Abstract. The physical property of the Hubbard model can be understood by solving the eigenvalue problem for the Hamiltonian derived from the model. Since the Hamiltonian is a large sparse matrix, an iteration method is usually utilized for solving the problems. One of effectual solvers for this problem is the LOBPCG (Locally Optimal Block Preconditioned Conjugate Gradient) method. The tuning strategies of the method on GPU systems when all iteration vectors are stored in device memory have been proposed. In this research, we propose tuning strategies for parallel LOBPCG method on multi-GPU system when the Hamiltonian is large and some iteration vectors are stored in host memory. When the LOBPCG method is used for solving multi eigenpairs (eigenvalues and the corresponding eigenvectors), the number of iteration vectors, whose size is the same as the dimension of the Hamiltonian, is proportional to the number of the eigenpairs. On the other hand, the memory consumption for the non-zero elements of the Hamiltonian can be significantly reduced by considering the regular arrangement of the elements. Therefore, when we execute the LOBPCG method for a large Hamiltonian on GPUs, some of the vectors have to be stored on host memory and have to be transferred between host and device memory as needed. Since the cost of the data transfer is very large, we also propose the optimization for it. The simulation result on a multi-GPU system shows that the optimization of the data transfer is very effective for high performance computing.

**Keywords:** LOBPCG method  $\cdot$  Multi-GPU systems  $\cdot$  Data transfer between CPU and GPU

# 1 Introduction

Eigenvalue problems appear in a variety of fields such as quantum dynamics, structure analysis and economics. Therefore, many solvers for them have been

developed and the strategies to improve their performance have also been proposed. In the quantum dynamics, when we solve eigenvalue problems derived from quantum models, we can recognize quantum states which indicate properties of the models. In this research, we focus on the eigenvalue problem for the Hamiltonian derived from the Hubbard model and will propose the strategies to realize a high performance solver on multi-GPU systems. The model can exhibit the property of many interesting phenomena such as high-temperature superconductivity [9,11], therefore, a lot of physicists take interest in it. The Hamiltonian, which represents the energy of the Hubbard model, is given as

$$H = -t \sum_{i,j,\sigma} c_{j\sigma}^{\dagger} c_{i\sigma} + \sum_{i} U_{i} n_{i\uparrow} n_{i\downarrow}, \qquad (1)$$

where t is the hopping parameter from a site to another one and  $U_i$  is the repulsive energy for one-site double occupation of two fermion the *i*-th site. Quantities  $c_{i,\sigma}, c_{i,\sigma}^{\dagger}$  and  $n_{i,\sigma}$  are the annihilation, the creation, and the number operator of a fermion with pseudo-spin  $\sigma$  on the *i*-th site, respectively. When we solve the ground state (the smallest eigenvalue and the corresponding eigenvector) of the Hamiltonian, we can understand the property of the model. Moreover, when we solve multi eigenpairs (eigenvalues and the corresponding eigenvectors), we can reveal more detail property. Therefore, many methods to solve the model have been proposed. One of the most accurate solvers is the exact diagonalization method which directly solves some eigenpairs of the Hamiltonian derived exactly from the model. At this time, the Hamiltonian becomes a huge sparse symmetric matrix. Accordingly, an iteration method, such as the Lanczos method and LOBPCG (Locally Optimal Block Preconditioned Conjugate Gradient) method [7,8], is usually utilized. And then, the parallelization strategies for multi-CPU systems [14] and the tuning ones for single-GPU systems [1, 12, 15, 17] have been proposed. In this research, in order to realize the LOBPCG method for solving some eigenpairs using multi-GPU systems, we will propose the parallelization and tuning strategies. The parallelization not only realizes speedup by distributing the calculations, but also enables simulations for larger models by distributing data. Since the memory size of GPU is generally smaller than that of CPU, we can calculate larger models by storing data in CPU memory (host memory) than in only GPU memory (device memory). Accordingly, in order to simulate a larger model, we transfer the data that are required for an operation from host to device memory and temporarily store them in device memory, and then, we execute the operation using them. Moreover, we have to transfer the calculation results from device to host memory, if necessary. Since the speed of the data transfer between host and device memory is much slower than that of data transfer in GPU, it is important to decrease the cost of data transfer between host and device memory for high performance parallel LOBPCG method on multi-GPU systems. In order to realize the decrease, we focus on the data transfer between host and device memory in this paper. Accordingly, although it may be possible to perform faster using CPUs in addition to GPUs, we target the LOBPCG method whose all time-consuming operations are performed on only GPUs.

The rest of the paper of structured as follows. Section 2 presents the implement schemes on multi-GPU systems. We propose the tuning strategies in view of data transfer between host and device memory in Sect. 3. Section 4 shows the result of numerical experiments on HPE SGI 8600 in Japan Atomic Energy Agency. A summary and conclusion are given in Sect. 5.

# 2 LOBPCG Method for Solving Multi Eigenpairs on Multi-GPU Systems

We can solve *m* eigenpairs of the matrix *H* using the LOBPCG method shown in Fig. 1<sup>1</sup>. The method requires *m* matrix-vector multiplications and some linear operations using iteration vectors  $\boldsymbol{x}_{k}^{(i)}$ ,  $\boldsymbol{w}_{k}^{(i)}$ ,  $\boldsymbol{p}_{k}^{(i)}$ ,  $\boldsymbol{\mathcal{X}}_{k}^{(i)}$ ,  $\boldsymbol{\mathcal{W}}_{k}^{(i)}$ , and  $\boldsymbol{\mathcal{P}}_{k}^{(i)}$

$$\begin{aligned} \mathbf{x}_{0}^{(i)} &:= \text{an initial guess}, \mathbf{p}_{0}^{(i)} := 0, i = 1, \dots, m \\ \mathbf{x}_{0}^{(i)} &= \mathbf{x}_{0}^{(i)} / || \mathbf{x}_{0}^{(i)} ||, i = 1, \dots, m \\ \mathbf{\mathcal{X}}_{0}^{(i)} &:= \mathbf{A}\mathbf{x}_{0}^{(i)}, \mathbf{\mathcal{P}}_{0}^{(i)} := 0, i = 1, \dots, m \\ \mathbf{\mathcal{X}}_{0}^{(i)} &:= (\mathbf{x}_{0}^{(i)}, \mathbf{\mathcal{X}}_{0}^{(i)}), \mathbf{w}_{0}^{(i)} := \mathbf{\mathcal{X}}_{0}^{(i)} - \mu_{-1}^{(i)} \mathbf{x}_{0}^{(i)}, i = 1, \dots, m \\ \text{do } k=0, \dots \text{ until convergence} \\ \mathbf{\mathcal{W}}_{k}^{(i)} &:= H \mathbf{w}_{k}^{(i)}, i = 1, \dots, m \\ S_{A} := \{\mathbf{x}_{k}^{(1)}, \dots, \mathbf{x}_{k}^{(m)}, \mathbf{W}_{k}^{(1)}, \dots, \mathbf{W}_{k}^{(m)}, \mathbf{p}_{k}^{(1)}, \dots, \mathbf{p}_{k}^{(m)} \}^{T} \\ \{\mathbf{\mathcal{X}}_{k}^{(1)}, \dots, \mathbf{\mathcal{X}}_{k}^{(m)}, \mathbf{\mathcal{W}}_{k}^{(1)}, \dots, \mathbf{\mathcal{W}}_{k}^{(m)}, \mathbf{p}_{k}^{(1)}, \dots, \mathbf{p}_{k}^{(m)} \}^{T} \\ \{\mathbf{x}_{k}^{(1)}, \dots, \mathbf{\mathcal{X}}_{k}^{(m)}, \mathbf{w}_{k}^{(1)}, \dots, \mathbf{w}_{k}^{(m)}, \mathbf{p}_{k}^{(1)}, \dots, \mathbf{p}_{k}^{(m)} \}^{T} \\ \{\mathbf{x}_{k}^{(1)}, \dots, \mathbf{x}_{k}^{(m)}, \mathbf{w}_{k}^{(1)}, \dots, \mathbf{w}_{k}^{(m)}, \mathbf{p}_{k}^{(1)}, \dots, \mathbf{p}_{k}^{(m)} \}^{T} \\ \{\mathbf{x}_{k}^{(1)}, \dots, \mathbf{x}_{k}^{(m)}, \mathbf{w}_{k}^{(1)}, \dots, \mathbf{w}_{k}^{(m)}, \mathbf{p}_{k}^{(1)}, \dots, \mathbf{p}_{k}^{(m)} \}^{T} \\ \{\mathbf{x}_{k}^{(1)}, \dots, \mathbf{x}_{k}^{(m)}, \mathbf{w}_{k}^{(1)}, \dots, \mathbf{w}_{k}^{(m)}, \mathbf{p}_{k}^{(1)}, \dots, \mathbf{p}_{k}^{(m)} \}^{T} \\ \{\mathbf{x}_{k}^{(1)}, \dots, \mathbf{x}_{k}^{(m)}, \mathbf{w}_{k}^{(1)}, \dots, \mathbf{w}_{k}^{(m)}, \mathbf{p}_{k}^{(1)}, \dots, \mathbf{p}_{k}^{(m)} \}^{T} \\ \{\mathbf{x}_{k+1}^{(1)} := \sum_{j=1}^{m} \{\mathbf{a}_{j}^{(i)}, \mathbf{x}_{2}^{(j)}, \dots, \mathbf{p}_{m}^{(m)}\}^{T} \\ \{\mathbf{x}_{k+1}^{(1)} := \sum_{j=1}^{m} \{\mathbf{a}_{j}^{(i)}, \mathbf{x}_{j}^{(j)}, \dots, \mathbf{p}_{k}^{(m)}, \mathbf{y}_{j}^{(i)}, \mathbf{y}_{j}^{(j)} \}, i = 1, \dots, m \\ \mathbf{y}_{k+1}^{(i)} := \sum_{j=1}^{m} \{\mathbf{a}_{j}^{(i)}, \mathbf{w}_{k}^{(j)} + \mathbf{y}_{j}^{(i)}, \mathbf{p}_{k}^{(j)} \}, i = 1, \dots, m \\ \mathbf{y}_{k+1}^{(i)} := \sum_{j=1}^{m} \{\mathbf{a}_{j}^{(i)}, \mathbf{w}_{k}^{(j)} + \mathbf{y}_{j}^{(j)}, \mathbf{p}_{k}^{(j)} \}, i = 1, \dots, m \\ \mathbf{y}_{k+1}^{(i)} := (\mathbf{x}_{k+1}^{(i)}, \mathbf{x}_{k+1}^{(i)})/(\mathbf{x}_{k+1}^{(i)}, \mathbf{x}_{k+1}^{(i)}), i = 1, \dots, m \\ \mathbf{w}_{k+1}^{(i)} := T^{(i)^{-1}}(\mathbf{\mathcal{X}_{k+1}^{(i)} - \mu_{k}^{(i)}, \mathbf{x}_{k+1}^{(i)}), i = 1, \dots, m \\ \mathbf{w}_{k+1}^{(i)} := T^{(i)^{-1}}(\mathbf{\mathcal{X}_{k+1}^{(i)} - \mu_{k}^{(i)}, \mathbf{x}_{k+1}^{(i)}), i = 1, \dots, m \\ \mathbf{w}_{k+$$

**Fig. 1.** LOBPCG method for solving the *m* smallest eigenvalues and the corresponding eigenvectors of a symmetric matrix *H*.  $T^{(i)}$  is a preconditioner for the *i*-th smallest eigenvalues. And  $\mathcal{X}_{k}^{(i)}$ ,  $\mathcal{P}_{k}^{(i)}$ , and  $\mathcal{W}_{k}^{(i)}$  are  $H\mathcal{X}_{k}^{(i)}$ ,  $Hp_{k}^{(i)}$ , and  $H\mathcal{W}_{k}^{(i)}$ , respectively. As convergence progresses, a set of iteration vectors  $\{\mathcal{X}_{k}^{(1)}, \ldots, \mathcal{X}_{k}^{(m)}, \mathcal{W}_{k}^{(1)}, \ldots, \mathcal{W}_{k}^{(m)}, p_{k}^{(1)}, \ldots, p_{k}^{(m)}\}$  becomes linearly dependent, and the general eigenvalue problem can not be solved. Therefore, in practice, we orthonormalize a set of the vectors to calculate the algorithm stably.

<sup>&</sup>lt;sup>1</sup> In practice, in order to improve the convergence property, it is advisable to set the parameter m larger than the number of eigenpairs which we want to find.

(i = 1, 2, ..., m). Moreover, in order to execute the LOBPCG method stably, we have to orthonormalize iteration vectors  $\boldsymbol{x}_k^{(i)}$ ,  $\boldsymbol{w}_k^{(i)}$  and  $\boldsymbol{p}_k^{(i)}$ . At this time,  $S_B$  becomes the identity matrix. The parallelization schemes of the multiplication for the Hubbard model on multi-CPU systems have been proposed [14]. In addition, the tuning strategies for single-GPU systems have been also proposed [12,15,17]. We propose the parallelization of the multiplication on multi-GPU systems by combining the above two strategies appropriately. Since the size of device memory is typically a fraction of that of host memory, it is supposed in this paper that we store only the information of the matrix H and 2m vectors  $(\boldsymbol{w}_k^{(i)}, \mathbf{and } \boldsymbol{\mathcal{W}}_k^{(i)}, i = 1, \ldots, m)$  in device memory and the other vectors  $(\boldsymbol{x}_k^{(i)},$  $\boldsymbol{\mathcal{X}}_k^{(i)}, \boldsymbol{p}_k^{(i)}$  and  $\boldsymbol{\mathcal{P}}_k^{(i)}$ ) in host memory. Here, the time-consuming operations of LOBPCG method are Hamiltonian matrix-vector multiplication operations and the vector operations (dot product, vector update and orthonormalization). In the following, we introduce the parallelization strategies in multi-GPU systems for each operation.

### 2.1 Hamiltonian Matrix-Vector Multiplications

When we solve m eigenpairs of the Hamiltonian, we have to operate m Hamiltonian-vector multiplications per iteration. Since each of these multiplications can be executed independently, we focus on parallelization and tuning strategies for one multiplication. The Hamiltonian is represented as

$$H = D + I_{\downarrow} \otimes A_{\uparrow} + A_{\downarrow} \otimes I_{\uparrow}, \tag{2}$$

where D is a diagonal matrix from the repulsive energy, and  $A_{\uparrow}(A_{\downarrow})$  is a sparse symmetric matrix from the hopping of the up-spin (down-spin). And,  $I_{\uparrow}(I_{\downarrow})$  is the identity matrix, dimension of which is the same as that of  $A_{\uparrow}(A_{\downarrow})$ . When the dimension of  $A_{\uparrow}(A_{\downarrow})$  is  $n_{\uparrow}(n_{\downarrow})$ , the dimension of the Hamiltonian H is  $n_{\uparrow} \times n_{\downarrow}$ . Since the dimension of  $A_{\uparrow}$  and  $A_{\downarrow}$  is much smaller than that of H, we store the non-zero elements of  $A_{\uparrow}$ ,  $A_{\downarrow}$  and D in device memory instead of the matrix H. Here, the multiplication of the Hamiltonian and vector is

$$Hv = Dv + (I_{\downarrow} \otimes A_{\uparrow})v + (A_{\downarrow} \otimes I_{\uparrow})v.$$

We transform the vector v to the matrix V as the following manner:

$$v = \begin{pmatrix} v_1 \\ v_2 \\ \vdots \\ v_{n_{\uparrow} \times n_{\downarrow}} \end{pmatrix} \to V = \begin{pmatrix} v_1 & v_{n_{\uparrow}+1} \cdots & v_{n_{\uparrow} \times (n_{\downarrow}-1)+1} \\ v_2 & v_{n_{\uparrow}+2} \cdots & v_{n_{\uparrow} \times (n_{\downarrow}-1)+2} \\ \vdots & \vdots & \vdots \\ v_{n_{\uparrow}} & v_{2n_{\uparrow}} & \cdots & v_{n_{\uparrow} \times n_{\downarrow}} \end{pmatrix},$$

(3)

and the diagonal elements of the matrix D to the matrix  $\overline{D}$  as the same manner. Here, the matrix-vector multiplication is change into the following matrix-matrix multiplication:

$$(HV)_{i,j} = \bar{D}_{i,j}V_{i,j} + \sum_{k} A_{\uparrow i,k}V_{k,j} + \sum_{k} A_{\downarrow j,k}V_{i,k},$$

where the subscript i, j of a matrix is the (i, j)-th element of the matrix. Since the matrix V is a dense matrix, we can execute the multiplications in parallel as follows:

**CAL 1:**  $Y^c = \overline{D}^c \odot V^c + A_{\uparrow} V^c$ , **COM 1:** all-to-all communication from  $V^c$  to  $V^r$ , CAL 2:  $Z^r = V^r A_\perp^T$ , **COM 2:** all-to-all communication from  $Z^r$  to  $Z^c$ , **CAL 3:**  $Y^{c} = Y^{c} + Z^{c}$ .

where the superscription c and r denotes the columnwise and rowwise partitioning in matrix data for the parallel calculation. And,  $\odot$  means an elementwise multiplication. The parallelization strategy requires two all-to-all communication operations per multiplication.

When all non-zero elements of the matrix H and the data of the decomposed matrices  $V^c$  and  $V^r$ , are stored in device memory, we can execute CAL 1, CAL 2 and CAL 3 by using the algorithms proposed for single-GPU systems [12,15,17]. Here, the storage layout of  $V^c$  and  $V^r$  should be row-major and column-major order, respectively, in order that  $A_{\uparrow}V^c$  and  $V^rA_{\downarrow}^T$  are performed with contiguous memory access. Therefore, the method requires the change of the storage layout of the matrix between column-major and row-major order, however, the operation can be executed with high performance by using the shared memory on GPU systems.

#### $\mathbf{2.2}$ **Vector Operations**

The vector operations in the LOBPCG method can be categorized into the following three groups:

- Dot product for constructing  $3m \times 3m$ -dimensional symmetric matrix ( $S_A$  in Fig. 1).

- Updating all column vectors of  $X_{k+1}$ ,  $P_{k+1}$ ,  $W_{k+1}$ ,  $\mathcal{X}_{k+1}$  and  $\mathcal{P}_{k+1}$ where  $X_{k+1} = (\boldsymbol{x}_{k+1}^{(1)}, \dots, \boldsymbol{x}_{k+1}^{(m)})$ ,  $W_{k+1} = (\boldsymbol{w}_{k+1}^{(1)}, \dots, \boldsymbol{w}_{k+1}^{(m)})$ ,  $P_{k+1} = (\boldsymbol{p}_{k+1}^{(1)}, \dots, \boldsymbol{p}_{k+1}^{(m)})$ ,  $\mathcal{X}_{k+1} = (\mathcal{X}_{k+1}^{(1)}, \dots, \mathcal{X}_{k+1}^{(m)}) (= HX_{k+1})$  and  $\mathcal{P}_{k+1} = (\mathcal{P}_{k+1}^{(1)}, \dots, \mathcal{P}_{k+1}^{(m)}) (= HP_{k+1})$ .

- Orthonormalization for all column vectors of  $X_{k+1}$ ,  $P_{k+1}$  and  $W_{k+1}$ .

We discuss the dot product and update for vectors first, then the orthonormalization of vectors.

Dot Product and Vector Update. The parallelization of dot product can be realized by calculating the partial sum of dot product on each process and performing the sum-reduction for the partial sum by MPLALLREDUCE in all processes. The parallelization of vector update operation can be realized by performing the 'axpy' operation for the decomposed vectors on each process without data communication between processors. When all vectors are stored

| dd=0.d0                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| do i=1,l                                                                                                                                                                                    |

| do k=1,m                                                                                                                                                                                    |

| $tat=cudamemcpy(dx, x(n^{*}(i-1)+1,k), n, cudamemcpyhosttodevice)$                                                                                                                          |

| $tat=cudamemcpy(dp, p(n^{*}(i-1)+1,k), n, cudamemcpyhosttodevice)$                                                                                                                          |

| enddo                                                                                                                                                                                       |

| do k=1,m                                                                                                                                                                                    |

| do j=1,m                                                                                                                                                                                    |

| $stat=cublasddot\_v2(h, n, dx(1,k), 1, dp(1,j), 1, dd0(k,j))$                                                                                                                               |

| enddo                                                                                                                                                                                       |

| enddo                                                                                                                                                                                       |

| $tat=cublasdaxpy_v2(h, m^*m, 1.d0, 1, dd0, 1, dd, 1)$                                                                                                                                       |

| enddo                                                                                                                                                                                       |

| dot0=dd                                                                                                                                                                                     |

| call mpi_allreduce(dot0,dot,)                                                                                                                                                               |

| (a) dot product $(x, p)$                                                                                                                                                                    |

| do i=1,l                                                                                                                                                                                    |

| do k=1,m                                                                                                                                                                                    |

| $stat=cudamemcpy(dx, x(n^{*}(i-1)+1,k), n, cudamemcpyhosttodevice)$                                                                                                                         |

| $stat=cudamemcpy(dp, p(n^{*}(i-1)+1,k), n, cudamemcpyhosttodevice)$                                                                                                                         |

| enddo                                                                                                                                                                                       |

| dtmp=0.d0                                                                                                                                                                                   |

| do k=1,m                                                                                                                                                                                    |

| do j=1,m                                                                                                                                                                                    |

| $\mathrm{stat}=\mathrm{cublasdaxpy}_\mathrm{v2}(\mathrm{h,n},eta_\mathrm{j}^\mathrm{(k)},\mathrm{w}((\mathrm{n}^*(\mathrm{i}	ext{-}1)	ext{+}1,\mathrm{j}),1,\mathrm{dtmp}(1,\mathrm{k}),1)$ |

| ${ m stat}={ m cublasdaxpy\_v2(h,n,\gamma_i^{(k)},pd((1,j),1,dtmp(1,k),1))}$                                                                                                                |

| enddo                                                                                                                                                                                       |

| $stat=cudamemcpy(p(n^{*}(i-1)+1,k), dtmp(1,k), n, cudamemcpydevicetohost)$                                                                                                                  |

| enddo                                                                                                                                                                                       |

| do k=1,m                                                                                                                                                                                    |

| do j=1,m                                                                                                                                                                                    |

| $tat = cublasdaxpy_v2(h,n,\alpha_i^{(k)},xd((1,j),1,dtmp(1,k),1))$                                                                                                                          |

| enddo                                                                                                                                                                                       |

| $stat=cudamemcpy(x(n^{*}(i-1)+1,k), dtmp(1,k), n, cudamemcpydevicetohost)$                                                                                                                  |

| enddo                                                                                                                                                                                       |

| enddo                                                                                                                                                                                       |

|                                                                                                                                                                                             |

(b) Vector update  $(\boldsymbol{p}_k^{(i)} \text{ and } \boldsymbol{x}_k^{(i)} \text{ in Fig. 1.})$

**Fig. 2.** Schematic CUDA Fortran codes of vector operations of the LOBPCG method for solving *m* eigenpairs on multi-GPU systems. Here, the number of tiles of the vectors is *l* and the dimension of each tiled vector is *n*. Therefore, the dimension of the decomposed vector on each process is  $l \times n$ . Here, h is cuBLAS library handle. And, x, p, dot and dot0 are stored in host memory and dx, dp, w,  $\alpha$ ,  $\beta$ ,  $\gamma$ , dd, dd0 and dtmp in device memory. The codes are simplified to indicate the relationship between the data transfer and the execution on a GPU. Therefore, the code should be extended appropriately to actually execute the LOBPCG method. Moreover, the data is transferred in one operation by packing data. on device memory, the vector operations can be parallelized straightforwardly. However, in this research, 4 matrices  $(X_k, \mathcal{X}_k, P_k \text{ and } \mathcal{P}_k)$  are stored in host memory, and the data have to be transferred to device memory. Therefore, we partition the vectors into some tiles and we transfer each tile of the vectors from host to device memory and execute the partial dot product operation on each tile (Fig. 2(a)) [10]. The vector update operation can be also executed using almost the same strategy (Fig. 2(b)). However, the operation requires transferring the updated vectors from device to host memory.

**Orthonormalization of Vectors.** Here, we discuss the orthonormalization of the iteration vectors  $\boldsymbol{x}_{k}^{(i)}$ ,  $\boldsymbol{p}_{k}^{(i)}$ , and  $\boldsymbol{w}_{k}^{(i)}$ . In order that we execute the LOBPCG method for solving multi eigenpairs stably, a set of the basis of the subspace spanned by all iteration vectors, that is, a set of all column vectors of  $X_k$ ,  $P_k$ , and  $W_k$ , should be linearly independent. Therefore, we should orthogonalize the basis per iteration. The orthogonalization can be realized by many methods such as the modified Gram-Schmidt (MGS) orthonormalization, TSQR, CholeskyQR, CholeskyQR2 and so on [2,4,13]. When we apply these methods for vectors directly, we have to transfer vectors stored in host memory. Therefore, we focus on the orthogonalization strategy for the LOBPCG method proposed by Hetmaniuk and Lehoueq (HL) [3,5]. The HL strategy is as follows:

- Here, we represent the eigenvector corresponding to the *i*-th smallest eigenvalue of  $S_A$  as  $\boldsymbol{v}^{(i)}$ . And, it is assumed that a set of vectors  $\{\boldsymbol{v}^{(1)}, \boldsymbol{v}^{(2)}, \ldots, \boldsymbol{v}^{(m)}\}$  is orthonormal, moreover, a set of all column vectors of the matrices  $X_k$ ,  $P_k$  and  $W_k$  in the *k*-th iteration is also orthonormal.

- When the (i, j)-th element of the matrices  $C^1$ ,  $C^2$  and  $C^3$  are defined as  $C^{(i,j)}_{(i,j)} = (\alpha_i^{(i)}), C^2_{(i,j)} = (\beta_j^{(i)})$  and  $C^3_{(i,j)} = (\gamma_i^{(i)})$ , that is,

$$\begin{pmatrix} C^1\\ C^2\\ C^3 \end{pmatrix} = (\boldsymbol{v}^{(1)}, \boldsymbol{v}^{(2)}, \dots, \boldsymbol{v}^{(m)}),$$

$X_{k+1}$  and  $P_{k+1}$  are calculated by

$$(X_{k+1}, P_{k+1}) = (X_k, W_k, P_k)C, \quad C = \begin{pmatrix} C^1 & 0 \\ C^2 & C^2 \\ C^3 & C^3 \end{pmatrix}.$$

Here, a set of all column vectors of matrices  $X_{k+1}$  becomes orthonormal.

- We decompose matrix C into QR using QR decomposition. When we calculate  $X_{k+1}$  and  $P_{k+1}$  using the following formula

$$(X_{k+1}, P_{k+1}) = (X_k, W_k, P_k)Q_k$$

all columns of  $X_{k+1}$  and  $P_{k+1}$  are orthonormal<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>  $X_{k+1}$  is the same as the above result, because a set of  $(\boldsymbol{v}^{(1)}, \boldsymbol{v}^{(2)}, \dots, \boldsymbol{v}^{(m)})$  is orthonormal.

- Next, we orthonormalize the column vectors of  $W_{k+1}$  against those of  $X_{k+1}$ and  $P_{k+1}$  using the classical Gram-Schmidt (CGS) method, that is,  $W_{K+1}$  is updated by the following formula [6]

$$W_{k+1} = (I - X_{k+1}X_{k+1}^T - P_{k+1}P_{k+1}^T)W_{k+1}.$$

(4)

The method requires much less all reduce communication operations than the MGS method.

– Finally, we orthonormalize a set of the columns vectors of  $W_{k+1}$  using the MGS method. The MGS method requires a lot of all reduce communication operations, however, the number of the operations in this case is reduced by about one-ninth compared to the orthonormalization of all column vectors of three matrices  $X_{k+1}$ ,  $P_{k+1}$  and  $W_{k+1}$ . Moreover, since we orthonormalize a set of only the column vectors of  $W_{k+1}$  stored in device memory, we do not need to transfer any vectors between host to device memory.

In this operation, when we find vectors to be a combination of other vectors, we eliminate them in this iteration. We show the schematic CUDA Fortran code for orthogonalizing the column vectors  $W_{k+1}$  against those of  $X_{k+1}$  and  $P_{k+1}$  in Fig. 3. The operation requires to transfer  $X_{k+1}$  and  $P_{k+1}$  from host to device memory twice.

**Performance.** Here, we examine the performance of these three operations using the above methods for solving the eigenvalue problems of the Hamiltonian derived from  $5 \times 4$ -site Hubbard model with 5 up-spins and 5 down-ones using 16 GPUs of 4 nodes on HPE SGI8600 in Japan Atomic Energy Agency. The details of the system are shown in Table 1. Here, the dimension of the Hamiltonian is 240,374,016, therefore, the dimension of a partitioned vector for each GPU is 15,023,376.

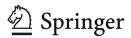

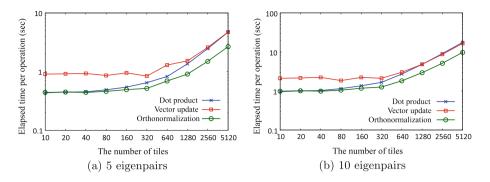

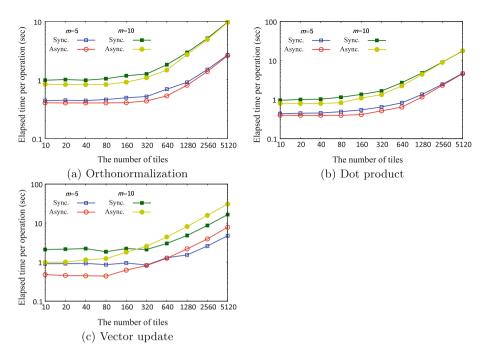

Figure 4 shows the elapsed time of each operation for solving 5 or 10 eigenpairs. The result indicates that the elapsed times tend to increase as the number of tiles becomes larger. The reason is that as the number of the tiles increases, the number of data transfer operations increases and the data size for each transfer operation decreases, that is, the latency of data transfer increases and the throughput declines. Moreover, in this result, it is noted that the elapsed time of the vector update operation is unstable. The reason is that when we execute operations on four GPUs on the system whose node logic diagram as shown in Fig. 5, we generally run two processes on each processor. When two processes on a processor simultaneously transfer data between host and device memory in the same direction, the bus connected between a CPU and two GPUs are shared with two processes and the throughput per process is limited to about half of the throughput of data transfer using one process. In the beginning of the iteration, the data transfer operations on two processes of one processor are synchronized. However, when the number of the tiles is large, that is, the number of iterations for completing the operation is large, the data transfer operations in the same direction on the two processes gradually become out of synchronization and the

```

do i=1.1

do k=1.m

stat=cudamemcpy(dx, x(n^{*}(i-1)+1,k), n, cudamemcpyhosttodevice)

stat=cudamemcpy(dp, p(n^{*}(i-1)+1,k), n, cudamemcpyhosttodevice)

enddo

do k=1,m

do j=1.m

stat=cublasddot v2(h, n, dx(1,k), 1, w((n*(i-1)+1,j), 1, dd0(k,j))

stat=cublasddot v2(h, n, dp(1,k), 1, w((n*(i-1)+1,j), 1, dd1(k,j)))

enddo

enddo

stat=cublasdaxpy v2(h, m*m, 1.d0, 1, dd0, 1, dh0,1)

stat=cublasdaxpy v2(h, m*m, 1.d0, 1, dd1, 1, dh1,1)

enddo

dot0=dh0

call mpi allreduce(dot0,dot,...)

dd0=dot

dot0=dh1

call mpi allreduce(dot0,dot,...)

dd1 = dot

do i=1.1

do k=1,m

stat=cudamemcpy(dx, x(n*(i-1)+1,k), n, cudamemcpyhosttodevice)

stat=cudamemcpy(px, p(n^{*}(i-1)+1,k), n, cudamemcpyhosttodevice)

enddo

do k=1,m

do j=1,m

stat= cublasdaxpy v2(h,n,dd0(k,j),dx(1,k),1,w((n*(i-1)+1,j),1))

stat= cublasdaxpy v2(h,n,dd1(k,j),dp(1,k),1,w((n*(i-1)+1,j),1))

enddo

enddo

enddo

```

Fig. 3. Schematic CUDA Fortran code of orthogonalizing the column vectors of W against those of X and P using the classical Gram-Schmidt method.

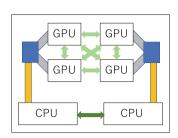

opposite directional transfer operations sometimes might be synchronized. They can be performed without conflict, and they achieve almost the same as the peak throughput when the size of the transferring data is large. Figure 6 shows their elapsed times for solving 10 eigenpairs. The result demonstrates that the elapsed time of the conventional method (synchronous data transfer) is in the interval between that of the same-directional data transfer with synchronization<sup>3</sup> and that of the opposite-directional one (Fig. 7). And, it is confirmed that the interval of throughput for the two data transfer operations becomes narrow as the number of tiles increases. The reason is that when transferring large data, the

<sup>&</sup>lt;sup>3</sup> MPL\_barrier operation is executed in the beginning of each iteration of the outermost loop in Fig. 2(b).

Fig. 4. Elapsed time of orthonormalization and dot product and vector update per operation.

Table 1. Details of GPU-system of HPE SGI 8600 in Japan Atomic Energy Agency.

| CPU                        | Intel Xeon Gold 6248R                                       |  |

|----------------------------|-------------------------------------------------------------|--|

|                            | $(3.0\mathrm{GHz},35.75\mathrm{MB}\mathrm{cache})$ × 2 CPUs |  |

| Number of CPUs per node    | 2                                                           |  |

| Number of cores per CPU    | 24                                                          |  |

| Memory of node             | 386 GB                                                      |  |

| GPU                        | NVIDIA Tesla V100 SXM2 $32{\rm GB}$ memory                  |  |

| Number of GPUs per node    | 4                                                           |  |

| Connection between CPU-GPU | $\times 16$ PCIe (16 Gbytes/s)                              |  |

| Network                    | 4 ports of 4 $\times$ EDR Infini Band interfeces            |  |

| Network Throughput         | $50 \mathrm{GB/s}(12.5 \mathrm{GB/s} \times 4)$             |  |

|                            | (one direction)                                             |  |

throughput of the opposite-directional data transfer is larger than that of the same-directional one, however, as the size of the transferring data per operation becomes small, that is, the number of tiles becomes larger, the former declines and ultimately becomes almost the same as the latter.

# 3 Optimization CPU-GPU Data Transfer

## 3.1 Asynchronous Data Transfer

When we execute the calculation consuming huge memory on a GPU, we have to transfer the necessary data from host to device memory (HtoD). The data transfer operation can be overlapped with the calculation on GPUs by using asynchronous data transfer. In actual, the dot product, the vector update and the orthonormalization operations shown in Sect. 2.2 can be overlapped with the data transfer using the multi-buffering strategy. Since the data transfer of the

**Fig. 5.** Node logic diagram of GPU system on HPE SGI8600 in Japan Atomic Energy Agency.

Fig. 6. Comparison of elapsed time of vector update operation using three types of data transfer.

```

call mpi_rank(rank,...)

do k=1,m

if (mod(rank,2).eq.0) call mpi_barrier(...)

HtoD data transfer

Vector update operations

i

if (mod(rank,2).eq.1) call mpi_barrier(...)

DtoH data transfer

enddo

```

Fig. 7. Schematic code of vector update operation with performing HtoD data transfer on one process of a CPU and DtoH transfer on the other process at the same time. Here, two processes are run on each processor and the MPI ranks of these processes are set to be contiguous.

dot product and the orthonormalization operations is only HtoD, the overlap can be realized using the double-buffering. Moreover, the update vector operation requires to transfer the updated vectors from device to host memory (DtoH) in addition to HtoD data transfer. Therefore, the overlap of data transfer and calculation in the operation can be realized by using the triple-buffering.

Here, we compare the performance of the three operations using the synchronous data transfer with that using the asynchronous one. Figure 8 shows the relationship between the elapsed time of each operations and the number of the tiles. The results indicate that the method using the asynchronous data transfer is faster than the method using synchronous one for the dot product and the orthonormalization operations. On the other hand, for the vector update operation, when the number of tiles is small, the asynchronous data transfer realizes speedup, however, it is confirmed that the performance becomes unstable as the number of tiles increases. As a result, when the number is large, there are cases where the speedup effect can not be obtained.

Fig. 8. Comparison of elapsed time using synchronous and asynchronous data transfer operations. Here, m means the number of eigenpairs to be solved.

### 3.2 Reduction of Data Transfers

After updating vectors, we orthonormalize the column vectors of  $W_{k+1}$ , and we calculate  $S_A$  using the dot product operations. The vector update operation requires HtoD transfer for four matrices  $X_k$ ,  $\mathcal{X}_k$ ,  $P_k$  and  $\mathcal{P}_k$ , and DtoH transfer for four updated matrices  $X_{k+1}$ ,  $\mathcal{X}_{k+1}$ ,  $P_{k+1}$  and  $\mathcal{P}_{k+1}$ . The column vectors of these four updated matrices will be used as is for the following calculations. On the other hand, the column vectors of  $W_{k+1}$  are the residual vectors, and they are modified by a preconditioning. Therefore, we can perform the dot product operations and the orthonormalization after applying preconditioner. However, when we apply a preconditioner which works elementwisely like point Jacobi preconditioner, we can modify the updated residual vectors elementwise. Accordingly, when we apply such a preconditioner or do not perform any preconditioning, we can calculate the partial sum of the dot products by using the subset of five matrices  $X_{k+1}$ ,  $\mathcal{X}_{k+1}$ ,  $W_{k+1}$ ,  $P_{k+1}$  and  $\mathcal{P}_{k+1}$  before the data is transferred to the host memory<sup>4</sup>. Therefore, we can calculate  $X_{k+1}W_{k+1}^T$  and  $P_{k+1}W_{k+1}^T$  which are used for the orthogonalization of the column vectors of  $W_{k+1}$  against those of  $X_{k+1}$  and  $P_{k+1}$  without the HtoD data transfer. However, when we execute the orthogonalization using the result of the dot product, we have to transfer  $X_{k+1}$

<sup>&</sup>lt;sup>4</sup> When we use the HL strategy, the column vectors of  $X_{k+1}$  and  $P_{k+1}$  are orthonormal. In this case, we do not need to calculate  $X_{k+1}X_{k+1}^T$ ,  $X_{k+1}P_{k+1}^T$  and  $P_{k+1}P_{k+1}^T$ .

and  $P_{k+1}$  from host to device memory. After the orthogonalization, we orthonormalize the column vectors of  $W_{k+1}$  against each other without any HtoD data transfer, and then, we obtain  $\mathcal{W}_{k+1}$  by m matrix-vector multiplication operations. So as to calculate the remaining dot products using the  $\mathcal{W}_{k+1}$ , we have to transfer  $X_{k+1}$  and  $P_{k+1}$  from host to device memory. Accordingly, we eliminate the number of the matrices which are transferred form host to device memory by four per iteration. In the following, the method is called 'Red 1'.

Next, we focus on the operation to orthogonalize the column vectors of  $W_{k+1}$  against those of  $X_{k+1}$  and  $P_{k+1}$ . When we orthogonalize the *i*-th column vector  $\boldsymbol{w}_{k+1}^{(i)}$ , we remove the projection of each column vector of  $X_{k+1}$  and  $P_{k+1}$  from  $\boldsymbol{w}_{k+1}^{(i)}$  using the result of the dot product. When we operate  $\boldsymbol{w}_{k+1}^{(i)}$  directly, we have to transfer  $X_{k+1}$  and  $P_{k+1}$  from host to device memory. In order to reduce this data transfer, we represent the operated vector  $\boldsymbol{w}_{k+1}^{(i)}$  as

$$\boldsymbol{w}_{k+1}^{(i),*} = \sum_{l} f_x(l,i) \boldsymbol{x}_{k+1}^{(l)} + \sum_{l} f_p(l,i) \boldsymbol{p}_{k+1}^{(l)} + \sum_{l} f_w(l,i) \boldsymbol{w}_{k+1}^{(l)}, \qquad (5)$$

and we operate the coefficients instead of calculating the vector  $\boldsymbol{w}_{k+1}^{(i)}$  directly. After the orthogonalization of the column vectors of  $W_{k+1}$  against those of  $X_{k+1}$  and  $P_{k+1}$ , the coefficients are set as  $f_x(l,i) = -(\boldsymbol{x}_{k+1}^{(l)}, \boldsymbol{w}_{k+1}^{(i)})$ ,  $f_p(l,i) = -(\boldsymbol{p}_{k+1}^{(l)}, \boldsymbol{w}_{k+1}^{(i)})$  and  $f_w(l,i) = 0 (l \neq i), 1(l = i)$ . In this operation, when we modify the vector by the operation  $\boldsymbol{t}^* = \boldsymbol{t} - (\boldsymbol{t}, \boldsymbol{s})\boldsymbol{s}$  for  $||\boldsymbol{s}|| = 1$ , the norm of  $\boldsymbol{t}^*$  is given by  $||\boldsymbol{t}^*|| = \sqrt{||\boldsymbol{t}||^2 - (\boldsymbol{t}, \boldsymbol{s})^2}$ . When the norm of a vector becomes smaller than the tolerance in the process of the orthogonalization, we consider the vector to be the combination of other vectors and we eliminate the vector. Afterwards, we execute the orthonormalization of a set of column vectors of  $W_{k+1}$  against each other using the MGS method. Here, we can calculate the dot product  $z_{i,j} = (\boldsymbol{w}_{k+1}^{(i)}, \boldsymbol{w}_{k+1}^{(j),*})$  by

$$\begin{split} z_{i,j} &= \left( \sum_{l} f_{x}(l,i) \boldsymbol{x}_{k+1}^{(l)} + \sum_{l} f_{p}(l,i) \boldsymbol{p}_{k+1}^{(l)} + \sum_{l} f_{w}(l,i) \boldsymbol{w}_{k+1}^{(l)}, \\ &\sum_{l} f_{x}(l,j) \boldsymbol{x}_{k+1}^{(l)} + \sum_{l} f_{p}(l,j) \boldsymbol{p}_{k+1}^{(l)} + \sum_{l} f_{w}(l,j) \boldsymbol{w}_{k+1}^{(l)} \right) \\ &= \sum_{l} f_{x}(l,i) f_{x}(l,j) + \sum_{l} f_{p}(l,i) f_{p}(l,j) \\ &+ \sum_{l} \sum_{s} f_{x}(l,i) f_{w}(s,j) (\boldsymbol{x}_{k+1}^{(l)}, \boldsymbol{w}_{k+1}^{(s)}) + \sum_{l} \sum_{s} f_{p}(l,i) f_{w}(s,j) (\boldsymbol{p}_{k+1}^{(l)}, \boldsymbol{w}_{k+1}^{(s)}) \\ &+ \sum_{l} \sum_{s} f_{w}(l,i) f_{x}(s,j) (\boldsymbol{w}_{k+1}^{(l)}, \boldsymbol{x}_{k+1}^{(s)}) + \sum_{l} \sum_{s} f_{w}(l,i) f_{p}(s,j) (\boldsymbol{w}_{k+1}^{(l)}, \boldsymbol{p}_{k+1}^{(s)}) \\ &+ \sum_{l} \sum_{s} f_{w}(l,i) f_{w}(s,j) (\boldsymbol{w}_{k+1}^{(l)}, \boldsymbol{w}_{k+1}^{(s)}). \end{split}$$

When  $||\boldsymbol{w}_{k+1}^{(j),*}|| = 1$ , the vectors  $\boldsymbol{w}_{k+1}^{(i),*}$  and  $\boldsymbol{w}_{k+1}^{(j),*}$  become orthogonal by calculating  $f_x(l,i) = f_x(l,i) - z_{i,j}f_x(l,j)$ ,  $f_p(l,i) = f_p(l,i) - z_{i,j}f_p(l,j)$  and  $f_w(l,i) = f_w(l,i) - z_{i,j}f_w(l,j)$  (l = 1, 2, ..., m). Accordingly, we can orthonormalize all column vectors of  $W_{k+1}$  without performing additional dot product operations<sup>5</sup>.

Therefore, the multiplication of the Hamiltonian and an orthonormalized vector  $\boldsymbol{w}_{k+1}^{(i),*}$  can be represented as

$$H\boldsymbol{w}_{k+1}^{(i),*} = \sum_{l} f_x(l,i) H\boldsymbol{x}_{k+1}^{(l)} + \sum_{l} f_p(l,i) H\boldsymbol{p}_{k+1}^{(l)} + \sum_{l} f_w(l,i) H\boldsymbol{w}_{k+1}^{(l)}.$$

(6)

Here, we calculate the remaining dot products  $(H\boldsymbol{x}_{k+1}^{(j)}, \boldsymbol{w}_{k+1}^{(i),*}), (H\boldsymbol{p}_{k+1}^{(j)}, \boldsymbol{w}_{k+1}^{(i),*})$ and  $(H\boldsymbol{w}_{k+1}^{(i),*}, \boldsymbol{w}_{k+1}^{(j),*})$  for constructing the matrix  $S_A$  using the coefficients and the results of the dot products in consideration of (5) and (6). Since the dot products except  $(H\boldsymbol{w}_{k+1}^{(i)}, \boldsymbol{w}_{k+1}^{(j)})$  have already been calculated during the vector update operation, we calculate  $(H\boldsymbol{w}_{k+1}^{(i)}, \boldsymbol{w}_{k+1}^{(j)})$  using  $H\boldsymbol{w}_{k+1}^{(i)} (= \boldsymbol{\mathcal{W}}_{k+1}^{(i)})$  obtained by executing matrix-vector multiplication. Therefore, we do not need to transfer extra matrix data from host memory for constructing  $S_A$ . After we solve the eigenvalue problem for  $S_A$ , we transfer four matrices  $X_{k+1}, \mathcal{X}_{k+1}, P_{k+1}$  and  $\mathcal{P}_{k+1}$  to update  $X_{k+2}, \mathcal{X}_{k+2}, P_{k+2}$  and  $\mathcal{P}_{k+2}$ . Before the update, we construct  $W_{k+1}(=(\boldsymbol{w}_{k+1}^{(1)*}, \dots, \boldsymbol{w}_{k+1}^{(m)*}))$  and  $\mathcal{W}_{k+1}(=(H\boldsymbol{w}_{k+1}^{(1)*}, \dots, H\boldsymbol{w}_{k+1}^{(m)*}))$  based on (5) and (6) using the transferred matrices and the coefficients  $f_x, f_p$  and  $f_w$ . As a result, the strategy can reduce HtoD data transfer for four matrices compared to 'Red 1'. In the following, the method is called 'Red 2'.

In order to evaluate the effect of the reduction of data transfers, we execute these two methods ('Red 1' and 'Red 2') and the conventional method ('Conv') described in Sect. 2 with the synchronous, the opposite-direction and the asynchronous data transfers under the same condition as in Sect. 2. Here, we set the number of tiles to be 20, and we execute the LOBPCG method with no preconditioner. And then, we show the elapsed time of the orthonormalization, the vector update and the dot product operations in Table 2. In 'Red1' and 'Red2' methods, some dot product operations are fused with other operations. Therefore, these elapsed times includes the elapsed time of the fused dot product operations. The result demonstrates that the reduction of the number of the data transfer between host and device memory can considerably improve the performance. Moreover, 'Red2' method can realize orthonormalization by operating the coefficients of (5) instead of calculating vectors directly, therefore, the method greatly reduce the elapsed time for orthonormalization.

<sup>&</sup>lt;sup>5</sup> This orthonormalization operation is equivalent to CholeskyQR method [13].

|                                    | Elapsed time (sec) |        |        |          |        |        |        |        |        |

|------------------------------------|--------------------|--------|--------|----------|--------|--------|--------|--------|--------|

|                                    | Sync.              |        |        | Opposite |        |        | Async. |        |        |

|                                    | Conv               | Red 1  | Red 2  | Conv     | Red 1  | Red 2  | Conv   | Red 1  | Red 2  |

| Orthonormalization<br>+dot product | 1.0128             | 0.5337 | 0.0008 | 1.0110   | 0.5330 | 0.0008 | 0.8321 | 0.4361 | 0.0008 |

| Vector update<br>+dot product      | 2.1547             | 2.5030 | 2.7597 | 1.4579   | 1.8501 | 2.1254 | 0.9734 | 1.4496 | 1.7005 |

| Remaining dot<br>product           | 1.0062             | 0.0158 | 0.0158 | 1.0037   | 0.0156 | 0.0156 | 0.7955 | 0.0158 | 0.0158 |

| Total                              | 4.1736             | 3.0525 | 2.7763 | 3.4726   | 2.3988 | 2.1419 | 2.6010 | 1.9015 | 1.7171 |

**Table 2.** Effect of reduction of data transfers. Here, 'Sync.', 'Opposite' and 'Async.' are represented as the synchronous data transfer, the opposite-directional one and the asynchronous one, respectively.

## 4 Numerical Experiments

In this section, we examine the performance of the LOBPCG method for the Hubbard model on the multi-GPU system in HPE SGI8600 in Japan Atomic Energy Agency. We solve the eigenvalue problems of the Hamiltonian derived from  $5 \times 4$ -site Hubbard model with 6 up-spins and 6 down-ones. The details of the system are shown in Table 1. Here, the dimension of the Hamiltonian is 1,502,337,600. We attempt to find the eight smallest eigenvalues and the corresponding eigenvectors using a block size of 10 columns. Accordingly, we use the convergence criterion

$$||H\boldsymbol{x}_{k}^{(i)} - \lambda(i)\boldsymbol{x}_{k}^{(i)}|| \leq 10^{-6}, \ i = 1, 2, \dots, 8,$$

where  $\lambda(i)$  is an approximate value of the *i*-th smallest eigenvalues. Here, we set the number of tiles to be 20 and use MPIDirect for communication for the matrixvector multiplication operation between GPUs. Moreover, we use the zero-shift preconditioner [14,16]. Since the preconditioner works elementwisely, we utilize 'Red 2' as the method for reducing of the data transfers. Table 3 shows the elapsed time of 'Red2' method using three types of data transfer. The result indicates that the synchronous data transfer method has the lowest performance of the three methods. The reason is that the conflict for the bus connected between CPU and two GPUs occurs due to performing the data transfer between host and device memory in the same direction simultaneously. The method using the opposite-directional data transfer is performed much faster than the synchronous one, because the method avoids the conflict by the opposite-directional data **Table 3.** Parallel performance of LOBPCG method on SGI HPE8600 system. This table shows the total elapsed time, the number of iterations, and the elapsed time per iteration of 'Red2' method using the synchronous, the opposite-direction and the asynchronous data transfer operations.

|                      | Elapsed time (sec) (top)                  |           |              |  |  |

|----------------------|-------------------------------------------|-----------|--------------|--|--|

|                      | Number of iterations (middle)             |           |              |  |  |

|                      | Elapsed time per iteration (sec) (bottom) |           |              |  |  |

|                      | Synchronous                               | Opposite  | Asynchronous |  |  |

| 32 GPUs              | 2295.8055                                 | 1927.8972 | 1426.4036    |  |  |

|                      | 205                                       | 205       | 205          |  |  |

|                      | 11.1991                                   | 9.4044    | 6.9581       |  |  |

| 64 GPUs              | 1233.4289                                 | 1067.7207 | 855.4724     |  |  |

|                      | 214                                       | 214       | 214          |  |  |

|                      | 5.7637                                    | 4.9893    | 3.9975       |  |  |

| $128 \mathrm{~GPUs}$ | 663.1469                                  | 582.9776  | 503.1989     |  |  |

|                      | 210                                       | 210       | 210          |  |  |

|                      | 3.1578                                    | 2.7761    | 2.3962       |  |  |

| $256 \mathrm{~GPUs}$ | 371.9728                                  | 332.6797  | 291.2728     |  |  |

|                      | 202                                       | 202       | 202          |  |  |

|                      | 1.8414                                    | 1.6469    | 1.4419       |  |  |

transfer operations. The method does not overlap the data transfer with the calculation, since its data transfer is a synchronous operation. On the other hand, the asynchronous method can overlap the data transfer with the calculation. Therefore, the method has better performance than the opposite-directional one.

Next, we show the elapsed time of 'conv', 'Red1' and 'Red2' methods using the asynchronous data transfer operation in Table 4. The result indicates that 'Red2' is the fastest. And, although Table 2 indicates that 'Red1' is more than 10% slower than 'Red2', 'Red1' is only a few percent slower in this result. The reason is that 'Red2' always requires m matrix-vector multiplication operations for calculating Hw by (6), whereas, since 'Red1' execute the operations for only independent linearly vectors, there is no need the multiplication for eliminated vectors by the orthonormalization operation. Table 4. Parallel performance of LOBPCG method on SGI HPE8600 system. This table shows the total elapsed time, the number of iterations, and the elapsed time per iteration of 'Conv', 'Red1' and 'Red2' methods using the asynchronous data transfer operation.

|                     | Elapsed time (sec) (top)                  |           |           |  |  |

|---------------------|-------------------------------------------|-----------|-----------|--|--|

|                     | Number of iterations (middle)             |           |           |  |  |

|                     | Elapsed time per iteration (sec) (bottom) |           |           |  |  |

|                     | Conv                                      | Red1      | Red2      |  |  |

| $32 \mathrm{~GPUs}$ | 2330.2672                                 | 1515.3687 | 1426.4036 |  |  |

|                     | 205                                       | 205       | 205       |  |  |

|                     | 11.3672                                   | 7.3920    | 6.9581    |  |  |

| 64 GPUs             | 1314.3161                                 | 857.6863  | 855.4724  |  |  |

|                     | 214                                       | 214       | 214       |  |  |

|                     | 6.1417                                    | 4.0079    | 3.9975    |  |  |

| 128 GPUs            | 657.6043                                  | 523.1674  | 503.1989  |  |  |

|                     | 210                                       | 210       | 210       |  |  |

|                     | 3.1314                                    | 2.4913    | 2.3962    |  |  |

| 256  GPUs           | 363.8983                                  | 296.9689  | 291.2728  |  |  |

|                     | 202                                       | 202       | 202       |  |  |

|                     | 1.8015                                    | 1.4701    | 1.4419    |  |  |

# 5 Conclusions

we have proposed the parallelization and the tuning strategies of the LOBPCG method, whose almost all operations are performed using GPUs, in order to solve an eigenvalue problem for a large Hamiltonian derived from the Hubbard model using multi-GPU systems. In this research, the dimension of the Hamiltonian is very large and some vectors are stored in host memory. In order to perform the calculations using GPUs in this situation, we have to transfer data between host and device memory as needed. The cost of the data transfer is very large. Therefore, we reduced the transfer operations by considering the algorithm of the LOBPCG method and achieved the improvement of the performance. Moreover, when we execute the conventional method using two processes on each processor on the system as shown in Fig. 5, two processes transfer data in the same direction at the same time. Accordingly, the bus connected between host and device memory is shared with two processes and the throughput per process is limited to about half of the peak throughput. In order to avoid sharing the bus, we have proposed the strategy in which two processes on each processor transfer data in opposite directions. The method has much better performance than the conventional one.

We proposed the strategies in consideration of the property of consuming a small amount of device memory to store Hamiltonian data. Therefore, the proposed strategies can be applied not only to eigenvalue problems for the Hamiltonian derived from the Hubbard model, but also to problems that consume a small amount of device memory to store matrix data or that do not require matrix data to be stored by calculating it per iteration.

In this research, since we mainly focused on the data transfer between host and device memory, all time-consuming operations, that is, matrix-vector multiplications and vector operations, have been executed using GPUs. Recently, the performance of a CPU is improving considerably. Therefore, it is possible to achieve better performance by performing some of calculations using CPUs, especially for problems with a lot of data transfer between host and device memory like the problem in this research. In future work, we plan to investigate the strategy to appropriately distribute the calculations to CPUs and GPUs.

Acknowledgments. This research was partially supported by JSPS KAKENHI Grant Number 18K11345. This research was conducted with the supercomputer HPE SGI8600 in the Japan Atomic Energy Agency.

# References

- Anzt, H., Tomov, S., Dongarra, J.: Accelerating the LOBPCG method on GPUs using a blocked sparse matrix vector product. In: Proceedings of the Symposium on High Performance Computing, pp. 75–82 (2015)

- Demmel, J., Grigori, L., Hoemmen, M., Langou, J.: Communication-optimal parallel and sequential QR and LU factorizations. SIAM J. Sci. Comput. 34, A206–A239 (2012). https://doi.org/10.1137/080731992

- Duersch, J.A., Gu, M., Shao, M., Yang, C.: A robust and efficient implementation of LOBPCG. SIAM J. Sci. Comput. 40, C655–C676 (2018). https://doi.org/10. 1137/17M1129830

- Furuya, T., Nakatsukasa, Y., Yanagisawa, Y., Yamamoto, Y.: CholeskyQR2: a simple and communication-avoiding algorithm for computing a Tall-Skinny QR factorization on a large-scale parallel system. In: ScalA 2014 (2014)

- Hetmaniuk, U., Lehoucq, R.: Basis selection in LOBPCG. J. Comput. Phys. 228, 324–332 (2006)

- Iwata, J.I., et al.: A massively-parallel electronic-structure calculations based on real-space density functional theory. J. Comput. Phys. 229, 2339–2363 (2010). https://doi.org/10.1016/j.jcp.2009.11.038

- Knyazev, A.V.: Preconditioned Eigensolvers an oxymoron? Electron. Trans. Numer. Anal. 7, 104–123 (1998)

- Knyazev, A.V.: Toward the optimal Eigensolver: locally optimal block preconditioned conjugate gradient method. SIAM J. Sci. Comput. 23, 517–541 (2001)

- Montorsi, A. (ed.): The Hubbard Model: A Collection on Reprints. World Scientific, Singapore (1992). https://doi.org/10.1142/1346

- Rabbi, F., Daley, C.S., Aktulga, H.M., Wright, N.J.: Evaluation of directive-based GPU programming models on a block Eigensolver with consideration of large sparse matrices. In: Wienke, S., Bhalachandra, S. (eds.) WACCPD 2019. LNCS, vol. 12017, pp. 66–88. Springer, Cham (2020). https://doi.org/10.1007/978-3-030-49943-3\_4

- Rasetti, M. (ed.): The Hubbard Model: Recent Results. World Scientific, Singapore (1991). https://doi.org/10.1142/1377

- Siro, T., Harju, A.: Exact diagonalization of the Hubbard model on graphics processing units. Comp. Phy. Comm. 183, 1884–1889 (2012)

- Stathopoulos, A., Wu, K.: A block orthogonalization procedure with constant synchronization requirements. SIAM J. Sci. Comput. 23, 2165–2182 (2006). https:// doi.org/10.1137/S1064827500370883

- Yamada, S., Imamura, T., Machida, M.: 16.447 TFlops and 159-billion-dimensional exact-diagonalization for trapped Fermion-Hubbard model on the earth simulator. In: Proceedings of SC05 (2005)

- Yamada, S., Imamura, T., Machida, M.: High performance eigenvalue solver in exact-diagonalization method for Hubbard model on CUDA GPU. In: Joubert, G.R., Leather, H., Parsons, M., Peters, F., Sawyer, M. (eds.) Parallel Computing: On the road to Exascale. Advances in Parallel Computing, vol. 27, pp. 361–369. IOS (2016). https://doi.org/10.3233/978-1-61499-621-7-361

- Yamada, S., Imamura, T., Machida, M.: Communication avoiding Neumann expansion preconditioner for LOBPCG method: convergence property of exact diagonalization method for Hubbard model. In: Bassini, S., Danelutto, M., Dazzi, P., Joubert, G.R., Peters, F. (eds.) Parallel Computing is Everywhere. Advances in Parallel Computing, vol. 32, pp. 27–36. IOS (2018). https://doi.org/10.3233/978-1-61499-843-3-27

- Yamada, S., Imamura, T., Machida, M.: High performance eigenvalue solver for Hubbard model: tuning strategies for LOBPCG method on CUDA GPU. In: Foster, I., Joubert, G.R., Kučera, L., Nagel, W.E., Peters, F. (eds.) Parallel Computing: Technology Trends. Advances in Parallel Computing, vol. 36, pp. 105–113. IOS (2020). https://doi.org/10.3233/APC200030

**Open Access** This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

# Vapor Condensation Under Electric Field: A Study Using Molecular Dynamics Simulation

Pengyu Wang<sup>(⊠)</sup> and Zhong Chen

School of Materials Science and Engineering, Nanyang Technological University, 50 Nanyang Avenue, Singapore 639798, Singapore n2007034k@e.ntu.edu.sg

**Abstract.** The condensation of water vapor on the substrate surface under electric field is studied by molecular dynamics simulation, and a series of behaviors of water molecules during condensation were studied, such as nucleation, growth and coalescence. In the process of condensation, there will be some small clusters, whose size increases with the increase of time, and under the action of the movement of water molecules in vapor, the clusters move irregularly on the substrate surface and coalesced into larger clusters. And the droplets will be stretched along the direction of the electric field. Interestingly, the condensation will decrease with the increase of the electric field strength under the electric field perpendicular to the surface. The results also show that the orientations of water molecule dipole are closely related to the direction of electric field, indicating that the electric intensity will have great impact on vapor condensation, which provides guidance for reversible adjustment of vapor condensation and the design of intelligent surface.

Keywords: Condensation  $\cdot$  Molecular dynamics simulation  $\cdot$  Electric field  $\cdot$  Cluster

# 1 Introduction

Vapor condensation is closely related to our daily life and can be utilized for water collection [1], thermal management [2], water desalination [3] and so on. Therefore, mechanism of water vapor condensation is very important for the rational utilization of condensation, and the efficient condensation has also attracted the interest of many researchers.

A large number of studies show that the roughness and chemical properties of the condensation surface have important impact on the condensation efficiency [4–9]. The development of molecular dynamics simulation provides a new method for the study of water molecular condensation. For example, Xu et al. studied the condensation of water vapor on the V-shaped groove by molecular dynamics simulation [4], the results show that the wetting modes of clusters are determined by the intrinsic contact angle and the cross sectional angle of the surface. Another study by the same team shows that the

formation and growth of clusters in the process of water vapor condensation increase with the increase of substrate hydrophilicity [5]. Gao et al. explored the condensation of water vapor on the nanostructured surfaces with hybrid wettability areas and found that the nanostructured surfaces with hybrid wettability areas has better heat transfer performance [6]. Huang et al. discussed the effects of pillar height, spacing and substrate wettability on argon condensation [7]. However, the influence of external field is ubiquitous and will have a great impact on the condensation of water vapor, such as electric, temperature, force.

At present, studies exist mainly on the influence of external electric field on the static and dynamic behavior of sessile droplets on the surface [10–15] and water evaporation [16]. The research of Yan et al. [10] shows that the voltage amplitude and frequency of tangential AC electric field are important factors affecting the dewetting of droplets. The dynamics behaviors of droplets on flexible graphene sheets under constant and alternating electric fields with different amplitudes and frequencies are studied by Kargar [11] et al., and the results show that droplets elongated in the direction of electric field. Wang et al. [12] simulated the condensation process of water molecules under the action of an electric field perpendicular to the surface by molecular dynamics simulation and found that the condensation could be inhibited by vertical electric field.

Water molecules are easy to be affected by electric field because of the polarity, and electric field is an easily available clean energy, which provides a premise for its large-scale utilization, such as electrostatic spray, electrohydrodynamic atomization. The existence of external field also provides a new method to dynamically regulate the condensation of water molecules. However, the mechanism of the vapor condensation under external field is still not well understood. In this paper, the condensation process of water molecules under constant electric field perpendicular to the surface is studied by molecular dynamics simulation. The growth of maximum cluster size, number of clusters, dipole moment and the temperature of water molecules are calculated to quantify the condensation process. The research results are also useful for the efficient utilization of heat and mass transfer.

# 2 Model and Methods

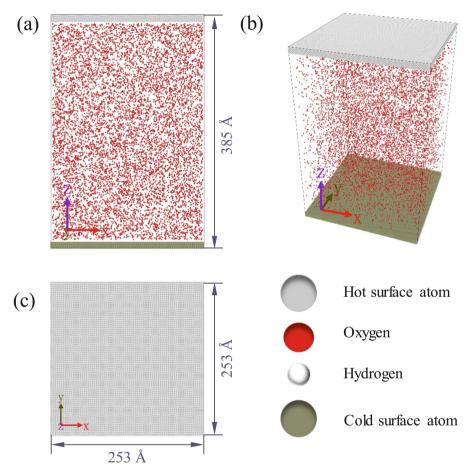

In this paper, the molecular dynamics simulation software LAMMPS is used to simulate the condensation process of water vapor under the action of electric field [17, 18]. The structure of the simulation system is shown in Fig. 1. The simulation system consists of three parts, including an upper substrate (hot surface), a lower substrate (cold surface) and water molecules. In order to improve the calculation efficiency, the structure of copper atoms is used to establish the models of the cold surface and hot surface, in which the lattice is 3.615 Å, the thickness of the cold surface and hot surface is 10.845 Å, and the lateral dimension is 253 \* 253 Å, consisting of 58800 atoms, [6, 19, 20]. Meanwhile, to improve the condensation rate of water molecules, 10000 water molecules are placed in the simulation systems.

The simple point charge/extension (SPC/E) model, which has been validated in previous studies, is chosen to describe the interaction between the water and water [21–23]. The calculation method of the interaction between water molecules in the model

is consistent with our previous research [21, 24]. The interaction between substrate atoms and water molecules is calculated by Lennard-Jones (L-J) potential, where the energy coefficient ( $\epsilon$ ) is 0.2 kJ/mol, and the distance coefficient ( $\sigma$ ) is 2.891 Å. The interaction between the substrate atoms is also described by the L-J potential, in which  $\epsilon_{S-S} = 4.72$  kJ/mol,  $\sigma_{S-S} = 2.616$  Å [25], and there is no interaction between the upper substrate atoms and lower substrate atoms. In the simulation, the cutoff distances are set as 12 Å.

**Fig. 1.** Schematic diagram for the simulation system. (a) Front view. (b) Perspective view. (c) Top view.

In the process of simulation, the periodic boundary conditions are applied in all directions. Meanwhile, the velocity-Verlet algorithm is used to solve the Newtonian motion equation with a time step of 1 femtosecond (fs). The particle–particle particle-mesh (PPPM) method is used to calculate the long-range electrostatic interactions with

an accuracy up to 10–4. And to improve the calculation efficiency, SHAKE algorithm is used to fix the bonds and angles of water molecules.

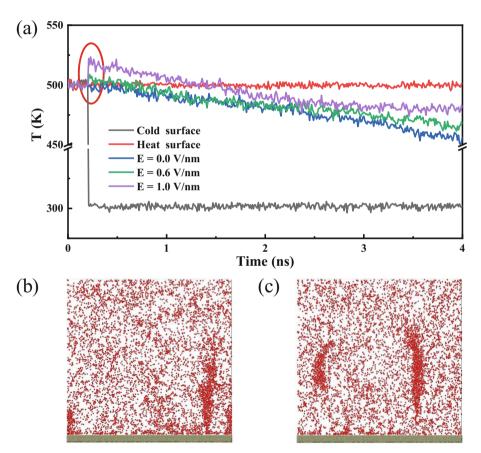

And all the simulations are performed in two stages: First, the equilibration phase is carried out for a total of 0.2 ns (ns) in a NVT ensemble, and the temperature of water molecules and substrate atoms are controlled at 500 K. Then the thermostat applied on the water vapor is removed, the temperatures of the lower and upper surfaces in the system are controlled at 300K and 500K, respectively. In order to observe the condensation of water molecules faster, the temperature difference of the substrates is set larger. At the same time, the electric field is applied to the system. In our study, constant electric field perpendicular to the surface is applied to study the effect of electric field on water vapor condensation. And the simulation time for condensation is extended to 4 ns to see the condensation process clearly.

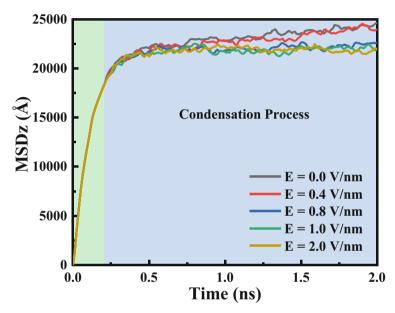

The growth of clusters is an important index to study the condensation process. In this study, the Stillinger criterion is used to define clusters, two water molecules are determined to be located in one cluster when the distance between oxygen atoms in two water molecules is 3.36 Å [26].

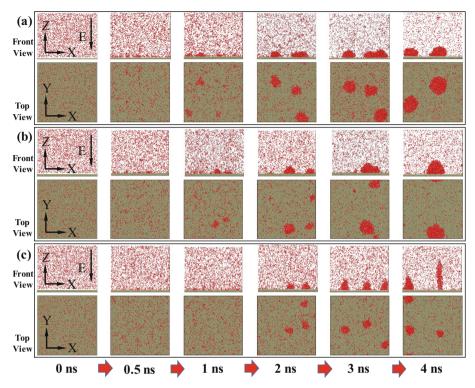

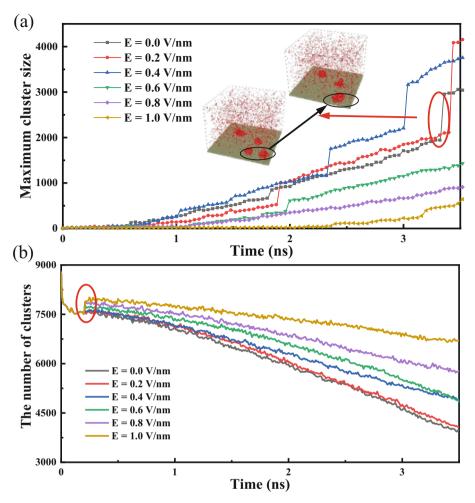

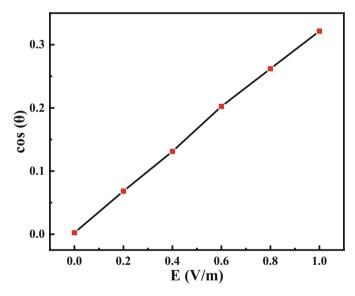

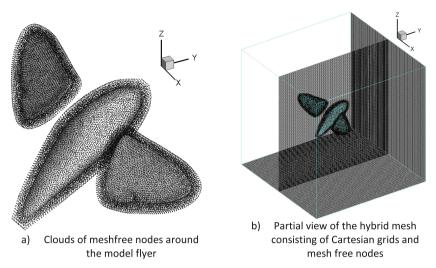

## **3** Results and Discussion