Nina Narodytska / Philipp Rümmer (Eds.)

# PROCEEDINGS OF THE 24TH CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2024

Nina Narodytska / Philipp Rümmer (Eds.) PROCEEDINGS OF THE 24TH CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2024

# Conference Series: Formal Methods in Computer-Aided Design Volume 5

Conference Series: Formal Methods in Computer-Aided Design

Series edited by: Warren A. Hunt, Jr., The University of Texas at Austin Austin, TX 78705 | hunt@cs.utexas.edu Georg Weissenbacher, TU Wien

Karlsplatz 13, 1040 Vienna, Austria | georg.weissenbacher@tuwien.ac.at

The Conference on Formal Methods in Computer-Aided Design (FMCAD) is an annual conference on the theory and applications of formal methods in hardware and system verification. FMCAD provides a leading forum to researchers in academia and industry for presenting and discussing groundbreaking methods, technologies, theoretical results, and tools for reasoning formally about computing systems. FMCAD covers formal aspects of computer-aided system design including verification, synthesis, and testing.

Information on this publication series and the volumes published therein is available at www.tuwien.ac.at/academicpress.

Volume 4 edited by:

Nina Narodytska, VMware by Broadcom, Palo Alto, USA | n.narodytska@gmail.com

Philipp Rümmer, University of Regensburg, Germany and Uppsala University, Sweden | philipp.ruemmer@ur.de

# PROCEEDINGS OF THE 24TH CONFERENCE ON FORMAL METHODS IN COMPUTER-AIDED DESIGN – FMCAD 2024

### Cite as:

Narodytska, N., & Rümmer, P. (Eds.). (2024). Proceedings of the 24th Conference on Formal Methods in Computer-Aided Design – FMCAD 2024. TU Wien Academic Press. https://doi.org/10.34727/2024/isbn.978-3-85448-065-5

# TU Wien Academic Press, 2024

c/o TU Wien Bibliothek TU Wien Resselgasse 4, 1040 Wien academicpress@tuwien.ac.at www.tuwien.at/academicpress

This work is licensed under a Creative Commons attribution 4.0 international license (CC BY 4.0). https://creativecommons.org/licenses/by/4.0/

ISBN (online): 978-3-85448-065-5 ISSN (online): 2708-7824

Available online: https://doi.org/10.34727/2024/isbn.978-3-85448-065-5

Media proprietor: TU Wien, Karlsplatz 13, 1040 Wien Publisher: TU Wien Academic Press Publication series editor: Warren A. Hunt, Jr. and Georg Weissenbacher Editors (responsible for the content): Nina Narodytska and Philipp Rümmer

# **Preface**

These are the proceedings of the twenty-fourth International Conference on Formal Methods in Computer-Aided Design (FMCAD), which was held in Prague, Czech Republic, October 14–18, 2024. The first FMCAD was organized in 1996, and FMCAD was a bi-annual conference until 2006, when the FMCAD and CHARME conferences merged into a single FMCAD. Since then, FMCAD has been an annual event. FMCAD 2024 was the twenty-fourth edition in the series, covering formal aspects of computer-aided system design including verification, specification, synthesis, and testing. It provided a leading forum to researchers in academia and industry to present and discuss groundbreaking methods, technologies, theoretical results, and tools for reasoning formally about computing systems. The program of FMCAD 2024 consisted of one tutorial, three invited talks, the presentation of the Hardware Model Checking Competition HWMCC'24, a student forum, and the main program consisting of presentations of 29 accepted peer-reviewed papers. FMCAD 2024 was co-located with the VSTTE 2024 conference, when took place on October 14–15.

The joint VSTTE/FMCAD tutorial day (October 15) featured two tutorials:

- The VSTTE tutorial: *The Lean Programming Language and Theorem Prover*, given by Sebastian Ullrich and Joachim Breitner:

- The FMCAD tutorial: Writing proofs in Dafny, given by Rustan Leino.

The main FMCAD conference (October 16–18) featured three invited talks:

- Tackling Scalability Issues in Bit-Vector Reasoning by Aina Niemetz;

- Some Adventures in Learning Proving, Instantiation and Synthesis by Josef Urban;

- Harnessing SMT Solvers for Reasoning about DeFi Protocols by Mooly Sagiv.

FMCAD 2024 received 56 submissions, out of which the committee decided to accept 29 for publication. Each submission received at least four reviews. The topics of the accepted papers include machine learning, model checking, hardware and software validation, SAT&SMT solving and proofs generation. Among the accepted papers, there are 26 regular papers (23 long and 3 short) and 3 tool/case study papers (all short). FMCAD 2024 hosted the twelfth edition of the FMCAD Student Forum, which has been held annually since 2013 and provides a platform for graduate students at any career stage to introduce their research to the FMCAD community. The FMCAD Student Forum 2024 was organized by Martin Blicha and Nestan Tsiskaridze and featured short presentations of 23 accepted contributions. The proceedings provide a detailed description of the Student Forum and lists all accepted contributions.

FMCAD 2024 was made possible by the support of a large number of people, as well as our sponsors. The program committee members and additional reviewers, listed on the following pages, did an excellent job providing detailed and insightful reviews. The reviews helped us build a strong program and helped the authors improve their submissions. We thank each and everyone of them for dedicating their time and providing their expertise. We would like to thank the local organization chair, Mikoláš Janota, and the registration chair, Milena Zeithamlová, who did an amazing job taking care of the organization and all practical matters. We thank our web master Julie Cailler, our sponsorship chair Guy Amir, and the Student Forum organizers Martin Blicha and Nestan Tsiskaridze. We thank the organizers of the HWMCC competition, Armin Biere, Nils Froleyks, and Mathias Preiner. We thank Georg Weissenbacher, both for his exceptional assistance in organizing the event, communicating to us the decisions of the steering committee, as well as being the publication chair.

Holding a conference like FMCAD would not be feasible without the financial support of our sponsors. We would like to express our gratitude to the sponsors, given here in alphabetical order: AWS, Cadence, General Electric Aerospace, Intel, NSF, Toyota, and VMware by Broadcom.

Last but not least, we thank all authors who submitted their papers to FMCAD 2024, and whose contributions and presentations form the core of the conference. The conference proceedings are available as Open Access Proceedings published by TU Wien Academic Press, and through the IEEE Xplore Digital Library.

We are grateful to everyone who presented their paper, gave a keynote or gave a tutorial. We thank all attendees of FMCAD for supporting the conference and making FMCAD an engaging and enjoyable event.

October 2024 Nina Narodytska VMware by Broadcom, USA

Philipp Rümmer University of Regensburg, Germany and

Uppsala University, Sweden

# Organizing Committee

**Program Co-Chairs**

Nina Narodytska VMware Research by Broadcom, CA, USA

University of Regensburg, Germany, Philipp Rümmer

and Uppsala University, Sweden

**Local Organization Chair**

Mikoláš Janota Czech Technical University in Prague, Czech Republic

**Registration Chair**

Milena Zeithamlová Action M Agency, Prague, Czech Republic

**Student Forum Chairs**

Martin Blicha Università della Svizzera italiana, Switzerland

Nestan Tsiskaridze Stanford University, CA, USA

Sponsorship Chair

Guy Amir Cornell University, NY, USA

Web Chair

Julie Cailler University of Regensburg, Germany

**Publication Chair**

TU Wien, Austria Georg Weissenbacher

# **FMCAD Steering Committee**

Clark Barrett Stanford University, CA, USA Armin Biere University of Freiburg, Germany

Ruzica Piskac Yale University, CT, USA Anna Slobodova Intel Corporation, TX, USA

Georg Weissenbacher TU Wien, Austria

# **Board of the FMCAD Association**

Armin Biere University of Freiburg, Germany

Roderick Bloem Graz University of Technology, Austria

Georg Weissenbacher TU Wien, Austria Florian Zuleger TU Wien, Austria

# **Program Committee**

# **FMCAD 2024 Program Committee**

Nina Narodytska (co-chair) VMware Research by Broadcom

Philipp Rümmer (co-chair) University of Regensburg

Guy Amir Cornell University

Mohamed Faouzi Atig Uppsala University

Jaroslav Bendík Certora

Armin Biere University of Freiburg

Per Bjesse Synopsys Inc. Nikolaj Bjørner Microsoft

Roderick Bloem Graz University of Technology Shaowei Cai Chinese Academy of Sciences

Rayna Dimitrova CISPA Helmholtz Center for Information Security

Rohit Dureja Advanced Micro Devices, Inc.

Gabriel Ebner Microsoft Research

Grigory Fedyukovich Florida State University

Alberto Griggio Fondazione Bruno Kessler

Arie Gurfinkel University of Waterloo

Liana Hadarean Amazon Web Services

William Harrison Idaho National Laboratory

Bo-Yuan Huang Intel Corporation

William Hung Cadence

Warren Hunt The University of Texas at Austin

Ahmed Irfan SRI International

Mikoláš Janota Czech Technical University in Prague

Daniela Kaufmann TU Wien

Tim King Google

Anna Lukina TU Delft

Andreas Lööw Imperial College London Ravi Mangal Colorado State University

Ken McMillan UT Austin

Baoluo Meng GE Aerospace Research CNRS / VERIMAG David Monniaux Alexander Nadel Technion & Intel Ruzica Piskac Yale University Mathias Preiner Stanford University Mohammad Rahmani Fadiheh Stanford University University of Iowa Andrew Reynolds Kristin Yvonne Rozier Iowa State University University of Freiburg Christoph Scholl

Natasha Sharygina University of Lugano, Switzerland Aditya A. Shrotri Siemens Digital Industries Software Carsten Sinz Karlsruhe University of Applied Sciences

Christoph Sticksel The MathWorks

Martin Suda Czech Technical University in Prague

Tachio Terauchi Waseda University Yakir Vizel The Technion

Tomáš Vojnar Brno University of Technology

Mike Whalen AWS

Thomas Wies New York University

Hongce Zhang Hong Kong University of Science and Technology (Guangzhou)

Shufang Zhu University of Liverpool

Florian Zuleger TU Wien

Ivana Černá Masaryk University

# FMCAD 2024 Student Forum Committee

Martin Blicha (co-chair) Università della Svizzera italiana

Nestan Tsiskaridze (co-chair) Stanford University

Guy Amir Cornell University

Haniel Barbosa Universidade Federal de Minas Gerais

Armin Biere University of Freiburg

Nikolaj Bjørner Microsoft

William Eiers Stevens Institute of Technology

Katalin Fazekas TU Wien

Alberto Griggio Fondazione Bruno Kessler Arie Gurfinkel University of Waterloo

Petra Hozzová Czech Technical University in Prague

Antti Hyvärinen Certora

Ahmed Irfan SRI International

Konstantin Korovin University of Manchester Daniel Larraz University of Iowa

Ondřej Lengál Brno University of Technology

Alexander Nadel Technion & Intel

Andres Noetzli Stanford University

Rodrigo Otoni Università della Svizzera italiana

Sophie Rain TU Wien

Mark Santolucito Barnard College, Columbia University

Christoph Sticksel The MathWorks

Hari Govind V. K. University of Waterloo & Microsoft

Yoni Zohar Bar Ilan University

# Additional Reviewers

Barbosa, Haniel Bogaerts, Bart Britikov, Konstantin

Brown, Chad

Cailler, Julie Chadha, Rohit Chvalovský, Karel

Dewes, Rafael

Esen, Zafer

Fazekas, Katalin Feng, Jincao Fleury, Mathias

Gauthier, Thibault Govind, R

Hamza, Ameer

He, Fei

Herrmann, Roland Hinnerichs, Tilman Holík, Lukáš

Hu, Guangyu

Isac, Omri

Kern, Philipp Kolárik, Tomáš Konrad, Alexander

Labbaf, Faezeh Lengal, Ondrej Li, Elaine

Lipparini, Enrico Lutz, Sterre

Maderbacher, Benedikt Mony, Hari Paul, Saswata

Rao, Vikas

Rebola Pardo, Adrian

Riley, Daniel

Rodriguez, Andoni Rogalewicz, Adam

Saivasan, Prakash Seufert, Tobias Sextl, Florian Sindoni, Giulia

Temel, Mertcan

Varanasi, Sarat Chandra

Zavalia, Lucas

# Table of Contents

| Tutorial                                                                     |    |

|------------------------------------------------------------------------------|----|

| Writing Proofs in Dafny                                                      | 1  |

| Invited Talks                                                                |    |

| Tackling Scalability Issues in Bit-Vector Reasoning                          | 2  |

| Some Adventures in Learning Proving, Instantiation and Synthesis             | 3  |

| Harnessing SMT Solvers for Reasoning about DeFi Protocols                    | 4  |

| Student Forum                                                                |    |

| The FMCAD 2024 Student Forum                                                 | 5  |

| Hardware Model Checking Competition                                          |    |

| Hardware Model Checking Competition 2024                                     | 7  |

| SMT Solving and Applications                                                 |    |

| Efficiently Synthesizing Lowest Cost Rewrite Rules for Instruction Selection | 8  |

| Extending DRAT to SMT                                                        | 18 |

| Solving String Constraints with Concatenation Using SAT                      | 29 |

| SMT-D: New Strategies for Portfolio-Based SMT Solving                        | 39 |

Modernizing SMT-Based Type Error Localization .....

Max Kopinsky, Brigitte Pientka, and Xujie Si

| Static Analysis                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Context Pruning for More Robust SMT-based Program Verification                                                                                                                                                                                                                      |

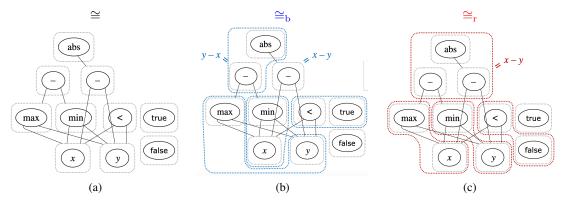

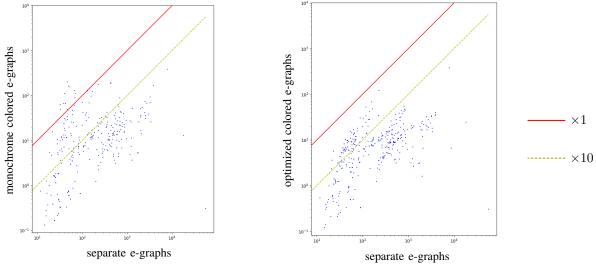

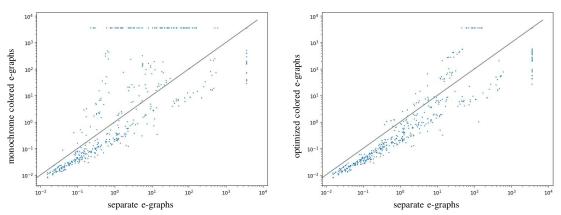

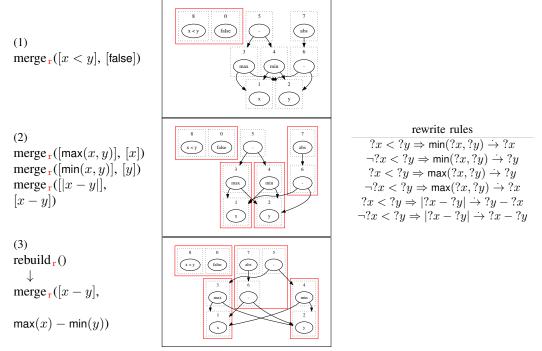

| Easter Egg: Equality Reasoning Based on E-Graphs with Multiple Assumptions                                                                                                                                                                                                          |

| Word Equations as Abstract Domain for String Manipulating Programs                                                                                                                                                                                                                  |

| Machine Learning in Verification                                                                                                                                                                                                                                                    |

| Formally Verifying Deep Reinforcement Learning Controllers with Lyapunov Barrier Certificates 95  Udayan Mandal, Guy Amir, Haoze Wu, Ieva Daukantas, Fletcher Lee Newell, Umberto  J. Ravaioli, Baoluo Meng, Michael Durling, Milan Ganai, Tobey Shim, Guy Katz, and Clark  Barrett |

| Leveraging LLMs for Program Verification                                                                                                                                                                                                                                            |

| Translating Natural Language to Temporal Logics with Large Language Models and Model Checkers119<br>Daniel Mendoza, Christopher Hahn, and Caroline Trippel                                                                                                                          |

| Verification I                                                                                                                                                                                                                                                                      |

| Recomposition: A New Technique for Efficient Compositional Verification                                                                                                                                                                                                             |

| Evaluating LLM-driven User-Intent Formalization for Verification-Aware Languages                                                                                                                                                                                                    |

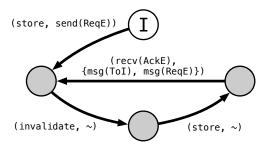

| Towards Verification Modulo Theories of asynchronous systems via abstraction refinement                                                                                                                                                                                             |

| Hardware                                                                                                                                                                                                                                                                            |

| Semi-open-state testing for in-silicon coherent interconnects                                                                                                                                                                                                                       |

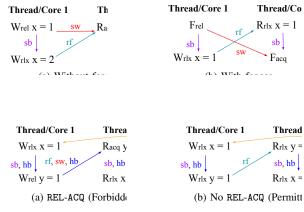

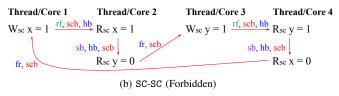

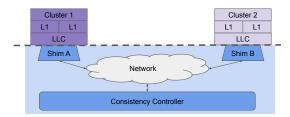

| Memory Consistency Model-Aware Cache Coherence for Heterogeneous Hardware                                                                                                                                                                                                           |

| Proofs and Certificates                                                                                                                                                                                                                                                             |

| Translating Pseudo-Boolean Proofs into Boolean Clausal Proofs                                                                                                                                                                                                                       |

| Verified Substitution Redundancy Checking                                                                                                                                                                                                                                           |

| Satisfiability Solving and Applications                                                                                                                                                                                                                                             |

Long-Hin Fung, Che Cheng, Yu-Wei Fan, Tony Tan, and Jie-Hong Roland Jiang

| Loris D'Antoni, Andrew Gacek, Amit Goel, Dejan Jovanović, Rami Gökhan Kıcı, Dan Peebles, Neha Rungta, Yasmine Sharoda, and Chungha Sung | 208 |

|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Toward Exhaustive Sequential Redundancy Removal                                                                                         |     |

| DAG-Based Compositional Approaches for LTLf to DFA Conversions                                                                          | 227 |

| Clausal Equivalence Sweeping                                                                                                            | 236 |

| Algorithms and Arithmetic                                                                                                               |     |

| Automatic Verification of Right-greedy Numerical Linear Algebra Algorithms                                                              | 242 |

| Formally Verified Rounding Errors of the Logarithm-Sum-Exponential Function                                                             | 251 |

| Symbolic Computer Algebra for Multipliers Revisited – It's All About Orders and Phases                                                  | 261 |

| Verification II                                                                                                                         |     |

| Combining Symbolic Execution with Predicate Abstraction and CEGAR                                                                       | 272 |

| Efficient Synthesis of Symbolic Distributed Protocols by Sketching                                                                      | 281 |

| Ownership in low-level intermediate representation                                                                                      | 292 |

# Writing Proofs in Dafny

K. Rustan M. Leino (D) Amazon Web Services Seattle, WA leino@amazon.com

Abstract-Dafny is a verification-aware programming language. In a nutshell, the language is Java-like and has support for writing specifications and proofs. It has a long history of being used in education, has been the cornerstone of several ambitious research projects, and is in industrial use at AWS.

This tutorial teaches how to write various kinds of proofs in Dafny. It covers proofs of imperative and functional programs, as well as the formalization of models and mathematical proofs. It demonstrates different proof styles and shows how to think about and debug proofs in the Dafny setting.

The tutorial does not assume any prior experience in using Dafny or other proof assistants.

# Tackling Scalability Issues in Bit-Vector Reasoning

Aina Niemetz (D) Stanford University Stanford, CA niemetz@cs.stanford.edu

Abstract—Efficiently reasoning about bit-vector constraints in Satisfiability Modulo Theories (SMT) has been an ongoing challenge for many years. The dominant state-of-the-art approach for solving bit-vector formulas in SMT is bit-blasting, an eager reduction to propositional logic that is typically combined with aggressive simplifications of the input constraints prior to the actual reduction step. Even though this eager reduction may come at the cost of significantly increasing the formula size, it is surprisingly efficient in practice—thanks to state-of-the-art SAT solvers, which are usually able to efficiently deal with complex formulas over millions of variables. This size increase, however, is a potential bottleneck and the main reason why bit-blasting does not generally scale well for increasing bit-widths, especially in the presence of arithmetic operators, which translate to large and complex Boolean circuits

To tackle these scalability issues, there are two (orthogonal) avenues to explore: developing alternative approaches that do not (mainly) rely on translations to the SAT level, and improving the scalability of bit-blasting itself. In this talk, we will highlight techniques in each category: a propagation-based local search procedure as an alternative to bit-blasting, which can only determine satisfiability but improves performances over bit-blasting on satisfiable instances, and a CEGAR-style abstraction-refinement procedure that significantly improves the scalability of bit-blasting. We extended the state-of-the-art SMT solver Bitwuzla with both techniques and show that they significantly improve solver performance on a variety of benchmark sets across all logics supported by Bitwuzla, including combinations of bit-vectors with arrays, uninterpreted functions and floating-point arithmetic.

# Some Adventures in Learning Proving, Instantiation and Synthesis

Josef Urban Czech Institute of of Informatics, Robotics and Cybernetics Prague, Czech Republic josef.urban@cvut.cz

Abstract—Human problem solvers often combine deductive reasoning and exploration with learning and pattern matching. In the recent years such combinations are also increasingly developed for building stronger automated theorem provers, SMT solvers and conjecturing and synthesis systems.

The methods in this field include equipping the current deductive systems with efficient statistically learned guidance that controls the choice of the inference steps, using for example fast decision trees, graph neural networks and their combinations.

Learning and AI methods can also be used to automatically design new symbolic strategies for today's ATPs and SMTs. This has the advantage of producing explainable ideas for steering the search space, which can be further taken up and modified by the systems' developers.

I will also discuss several methods that try to directly synthesize reasoning objects such as instantiations and OEIS explanations, using various neural approaches.

Perhaps the most interesting aspect of this research are the positive feedback loops between the proving and the learning methods. I will show that some of them can today go quite far and create quite interesting "alien" solutions.

# Harnessing SMT Solvers for Reasoning about DeFi **Protocols**

Mooly Sagiv Certora and Tel Aviv University Tel Aviv, Israel msagiv@acm.org

Abstract—DeFi (Decentralized Financial) Protocols implement financial programs using low-level programming. DeFi adoption started to go parabolic in 2020, and it's still very robust in different market conditions in 2024. Today, DeFi assets exceed 300 billion USD. A fundamental principle behind DeFi is that small open-source software called "smart contracts" precisely define the trading conditions and create an open global economy not controlled by governments and people.

However, smart contracts are difficult to implement correctly since their behavior can radically change in different market conditions. Moreover, hackers constantly try to abuse the code to drain the money stored in the smart contracts. On the positive side, it is pretty natural to write high-level formal specifications of smart contracts since their economical utilities are well understood. Indeed, this is a unique domain where software developers are eager to write formal specifications.

I will describe the challenges of harnessing existing SMT solvers for reasoning about smart contracts.

# The FMCAD 2024 Student Forum

Martin Blicha (1)

University of Lugano & Ethereum Foundation Prague, Czechia martin.blicha@usi.ch

Nestan Tsiskaridze (D) Stanford University Stanford, USA nestan@stanford.edu

Abstract-The Student Forum at the International Conference on Formal Methods in Computer-Aided Design (FMCAD) gives undergraduate and graduate students the opportunity to introduce their research to the Formal Methods community and receive feedback. In 2024, the event took place in Prague, Czechia. Twenty three students were invited to give a short talk and present a poster of their work.

Since 2013, the FMCAD Student Forum provides a platform for undergraduate and graduate students at any career stage to present their research to the audience of the FMCAD conference. The 2024 edition of the FMCAD Student Forum follows the tradition of its predecessors, which took place in:

- Portland, Oregon, USA in 2013 [1]

- Lausanne, Switzerland in 2014 [2]

- Austin, Texas in 2015 [3] and 2018 [4]

- Mountain View, California, USA in 2016 [5]

- Vienna, Austria in 2017 [6]

- San Jose, California, USA in 2019 [7]

- Virtual in 2020 [8] and 2021 [9]

- Trento, Italy in 2022 [10]

- Ames, Iowa, USA in 2023 [11]

FMCAD 2024 hosted the twelves edition of the Student Forum. Graduate and undergraduate students were invited to submit two-page reports of their current research and ongoing work in the scope of the FMCAD conference. There were 24 submissions to the forum, 23 of them were accepted one of which was withdrown. The Student Forum program committee reviews were based on the overall quality, novelty of the work, its potential impact on the Formal Methods community, as well as the potential positive impact on the student to have the opportunity to participate in the forum. The accepted submissions covered a wide range of topics relevant to the FMCAD community, from foundational aspects of automated reasoning, to analysis and verification of software, hardware, and neural networks, as well as applications of formal methods to security and dynamical system. Each submission received 3 reviews. The following contributions have been accepted<sup>1</sup> (excluding the withdrawn contribution):

- Csanád Telbisz and Dániel Szekeres Correctness Witnesses for Concurrent Software Verification

- Levente Bajczi and Marian Lingsch-Rosenfeld Software Verification Witnesses for Weak Memory

- Levente Bajczi CHCs for Weak Memory

<sup>1</sup>Only student authors listed for brevity.

- Islam Hamada Incremental Construction of Inductive Invariants for Model Checking

- Zsófia Ádám, Levente Bajczi, Marek Jankola and Marian Lingsch-Rosenfeld Towards Validation of More Expressive Software Non-Termination Witnesses

- Luke Miga Verifying Axiomatic Microarchitectural Models in the Coq Proof Assistant

- Konstantin Britikov Analysis of Multiloop Programs With Nested Loops Using Transition Power Abstraction

- Rachel Cleaveland Theory of Strings in Symbolic Execu-

- Siddharth Priya Optimizing Rust Programs Using Own-

- Daneshvar Amrollahi Towards Improved Stability for SMT Solvers

- John Kolesar Coinductive Proofs of Regular Expression Equivalence in Zero Knowledge

- Feitong Qiao Timed Data Types for Hardware

- Elizaveta Pertseva and Alex Ozdemir Multimodular Reasoning for Satisfiability Modulo Theories

- Fuqi Jia A Theory-Agnostic SMT Sampling Framework

- Milan Ganai Hamilton-Jacobi Reachability Estimation

- Samantha Archer SymLeak: Quantifying Side Channel Leakage with Symbolic Execution

- Daniel Mendoza Towards LLM-assisted hardware verification

- Edward Wang Work-in-Progress: An SMT-Based, Correct-by-Construction Place-and-Route Framework

- Michal Hečko Automata-based Decision Procedure for Presburger Arithmetic Augmented with Algebraic Rea-

- Áron Ricardo Perez-Lopez and Samantha Archer Word-Level Model Checking with IC3 in Pono

- Roxana-Mihaela Timon Verification of a dynamic programming-based algorithm for the Activity Selection Problem in Dafny

- Márk Somorjai and Mihály Dobos-Kovács Stack Abstraction for Interprocedural Software Verification

We formed a program committee to cover a wide range of topics so students could receive expert feedback on their work. The 2024 FMCAD Student Forum program committee consisted of Martin Blicha (co-chair), Nestan Tsiskaridze (cochair), Guy Amir, Haniel Barbosa, Armin Biere, Nikolaj Bjørner, William Eiers, Katalin Fazekas, Alberto Griggio,

Arie Gurfinkel, Petra Hozzová, Antti Hyvärinen, Ahmed Irfan, Konstantin Korovin, Daniel Larraz, Ondřej Lengál, Alexander Nadel, Andres Noetzli, Rodrigo Otoni, Sophie Rain, Mark Santolucito, Christoph Sticksel, Hari Govind V. K., and Yoni Zohar.

We would like to thank the organizers of FMCAD, as well as the FMCAD Student Forum program committee, who have made the FMCAD Student Forum possible. We would like to thank FMCAD, NSF, Amazon Web Services, Cadence, GE Aerospace, Intel, Toyota, and VMWare for providing student travel support and making it possible to award travel grants to all students. Additionally, we are grateful to the student authors and their research mentors who have contributed their excellent work to the program.

### REFERENCES

- [1] T. Wahl, "The FMCAD graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2013, Portland, OR, USA, October 20-23, 2013. IEEE, 2013, pp. 16–17. [Online]. Available: https://doi.org/10.1109/FMCAD.2013.7035523

- [2] R. Piskac, "The FMCAD 2014 graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2014, Lausanne, Switzerland, October 21-24, 2014. IEEE, 2014, p. 13. [Online]. Available: https://doi.org/10.1109/FMCAD.2014.6987589

- [3] G. Weissenbacher, "The FMCAD 2015 graduate student forum," in Formal Methods in Computer-Aided Design, FMCAD 2015, Austin, Texas, USA, September 27-30, 2015, R. Kaivola and T. Wahl, Eds. IEEE, 2015, p. 8. [Online]. Available: https://doi.org/10.1109/FMCAD.2015.7542246

- [4] D. Jovanović and A. Reynolds, "The FMCAD 2018 graduate student forum," in 2018 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2018, pp. 1–1, https://www.cs.utexas.edu/users/hunt/FMCAD/ FMCAD18/student-forum/.

- [5] H. Hojjat, "The FMCAD 2016 graduate student forum," in Formal Methods in Computer-Aided Design (FMCAD), 2016. IEEE, 2016, pp. 8–8, https://fmcad.forsyte.at/FMCAD16/student-forum.html.

- [6] K. Heljanko, "The FMCAD 2017 graduate student forum," in Proceedings of the 17th Conference on Formal Methods in Computer-Aided Design. FMCAD Inc, 2017, pp. 10–10, https://fmcad.org/FMCAD17/student-forum/.

- [7] G. Fedyukovich, "The FMCAD 2019 student forum," in 2019 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2019, pp. 1–1, https://fmcad.forsyte.at/FMCAD19/student-forum/.

- [8] P. Schrammel, "The FMCAD 2020 student forum," in 2020 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2020, pp. 1–1, https://fmcad.forsyte.at/FMCAD20/student-forum/.

- [9] M. Santolucito, "The FMCAD 2021 student forum," in 2021 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2021, pp. 1–1, https://fmcad.org/FMCAD21/student\_forum/.

- [10] M. Preiner, "The FMCAD 2023 student forum," in 2022 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2022, pp. 1–1, https://fmcad.org/FMCAD22/student\_forum/.

- [11] M. Janota and N. Narodytska, "The FMCAD 2023 student forum," in 2023 Formal Methods in Computer Aided Design (FMCAD). IEEE, 2023, pp. 1–1, https://fmcad.org/FMCAD23/student\_forum/.

# Hardware Model Checking Competition 2024

Armin Biere University of Freiburg Freiburg, Germany biere@cs.uni-freiburg.de

Nils Froleyks Johannes Kepler University Linz, Austria nils.froleyks@jku.at

Mathias Preiner Stanford University Stanford, United States preiner@cs.stanford.edu

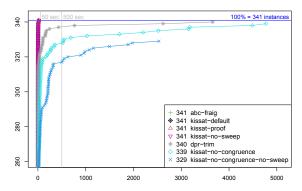

Abstract—The Hardware Model Checking Competition 2024 (HWMCC'24) was the 12th competitive event for hardware model checking tools. The competition was affiliated to the 24th conference on Formal Methods in Computer-Aided Design 2024 (FMCAD'24), which took place in Prague, Czech Republic, from October 14 to 18, 2024.

Index Terms—Automated Reasoning, Model Checking, Hardware Verification, Word-level Reasoning, Bit-Vectors, Certificates

The Hardware Model Checking Competition (HWMCC'24) in 2024 is the 12<sup>th</sup> incarnation in this series of competitive events to evaluate hardware model checking. Since it started in 2007 it was repeated annually with some exceptions. After the previous competition in 2020 the organizers took a break to resume the competition in 2024. The competition in 2024 is affiliated, as most of the time, with the conference on Formal Methods in Computer-Aided Design (FMCAD), which is considered the primary venue for formal hardware verification. Alternatively in 2007, 2008, 2010 and 2014 it was affiliated with the conference of Computer-Aided Verification (CAV).

The previous competition in 2020 continued with wordlevel tracks, which were introduced in 2019. These word-level tracks focus on bit-vector models with and without arrays in the BTOR2 format [1]. This suggests that model checkers participating in this track should make use of SMT solvers over the theory of bit-vectors. Before 2019 all competition tracks used bit-level models in the AIGER format [2], but were split into safety, multi-property, liveness and deep tracks. Since 2014 and particularly in 2017, the last competition before 2019, the ABC tool [3] dominated almost all bit-level tracks.

One motivation for moving to word-level tracks is the conjecture that SMT solving is more effective than plain SAT solving if the models are given in terms of bit-vectors. However, in 2019 the word-level model checkers could not fulfill this promise and were trailing ABC by a large margin in terms of performance. This was particularly the case for unsatisfiable properties, where a bad state violating the single safety property can not be reached. Note, that ABC was run on AIGER models obtained from the BTOR2 models through bitblasting, except for the array track, as bit-blasting of BTOR2 models with arrays is difficult. Having arrays, modelling memory or caches, is considered a feature of SMT solvers and should give them an advantage over bit-level reasoning.

In 2020 the picture changed and word-level model checkers started to become competitive to ABC on the bit-vector track without arrays, while not losing their advantage on bitvector models with arrays, as bit-blasting arrays was still not available. Therefore, the organizers of HWMCC'24 decided to continue both word-level tracks, i.e., with and without arrays.

While the previous competition in 2020 focused on wordlevel exclusively, the single safety property track came back in 2024. However, as a novel feature, participating model checkers are required to produce model-checking certificates. These certificates were actually AIGER circuits and should have an inductive property. They further need to simulate the original circuit as formalized in [4], [5], [6]. The tool CERTIFAIGER is used to check both requirements using SAT solvers. The goal of the certified track is to increase trust in verification results produced by model checkers, following the success story of proof producing SAT solvers in both academia and industry, e.g., producing proofs became mandatory in the main track of the SAT competition in 2016 [7].

More details on the competition, including provided tools, submission procedure and deadlines, the results and their presentation are available at the competition home page [8].

### REFERENCES

- [1] A. Niemetz, M. Preiner, C. Wolf, and A. Biere, "Btor2, BtorMC and Boolector 3.0," in Computer Aided Verification - 30th International Conference, CAV 2018, Held as Part of the Federated Logic Conference, FloC 2018, Oxford, UK, July 14-17, 2018, Proceedings, Part I, ser. Lecture Notes in Computer Science, H. Chockler and G. Weissenbacher, Eds., vol. 10981. Springer, 2018, pp. 587-595.

- [2] A. Biere, K. Heljanko, and S. Wieringa, "AIGER 1.9 and beyond," Institute for Formal Models and Verification, Johannes Kepler University, Altenbergerstr. 69, 4040 Linz, Austria, Tech. Rep. 11/2, 2011.

- [3] R. K. Brayton and A. Mishchenko, "ABC: an academic industrial-strength verification tool," in Computer Aided Verification, 22nd International Conference, CAV 2010, Edinburgh, UK, July 15-19, 2010. Proceedings, ser. Lecture Notes in Computer Science, T. Touili, B. Cook, and P. B. Jackson, Eds., vol. 6174. Springer, 2010, pp. 24-40.

- [4] E. Yu, N. Froleyks, A. Biere, and K. Heljanko, "Stratified certification for k-induction," in 22nd Formal Methods in Computer-Aided Design, FMCAD 2022, Trento, Italy, October 17-21, 2022, A. Griggio and N. Rungta, Eds. IEEE, 2022, pp. 59-64.

- -, "Towards compositional hardware model checking certification," in Formal Methods in Computer-Aided Design, FMCAD 2023, Ames, IA, USA, October 24-27, 2023, A. Nadel and K. Y. Rozier, Eds. IEEE, 2023, pp. 1-11.

- [6] N. Froleyks, E. Yu, A. Biere, and K. Heljanko, "Certifying phase abstraction," in Automated Reasoning - 12th International Joint Conference, IJCAR 2024, Nancy, France, July 3-6, 2024, Proceedings, Part I, ser. Lecture Notes in Computer Science, C. Benzmüller, M. J. H. Heule, and R. A. Schmidt, Eds., vol. 14739. Springer, 2024, pp. 284-303.

- T. Balyo, M. J. H. Heule, and M. Järvisalo, "SAT Competition 2016: Recent developments," in Proceedings 31st AAAI Conference on Artificial Intelligence, February 4-9, 2017, San Francisco, California, USA, S. Singh and S. Markovitch, Eds. AAAI Press, 2017, pp. 5061–5063.

- [8] A. Biere, N. Froleyks, and M. Preiner, 2024. [Online]. Available: https://hwmcc.github.io/2024/

# Efficiently Synthesizing Lowest Cost Rewrite Rules for Instruction Selection

Ross Daly Stanford University Stanford, CA, USA

rdaly525@cs.stanford.edu

Jackson Melchert Stanford University Stanford, CA, USA

melchert@stanford.edu

(iD)

Pat Hanrahan Stanford University Stanford, CA, USA

hanrahan@cs.stanford.edu

Caleb Donovick Stanford University Stanford, CA, USA

donovick@cs.stanford.edu

Priyanka Raina Stanford University Stanford, CA, USA

praina@stanford.edu

Caleb Terrill Stanford University Stanford, CA, USA cdterrill26@gmail.com

> Clark Barrett Stanford University Stanford, CA, USA

barrett@cs.stanford.edu

Abstract—Compiling programs to an instruction set architecture (ISA) requires a set of rewrite rules that map patterns consisting of compiler instructions to patterns consisting of ISA instructions. We synthesize such rules by constructing SMT queries, whose solutions represent two functionally equivalent programs. These two programs are interpreted as an instruction selection rewrite rule. Existing work is limited to singleinstruction ISA patterns, whereas our solution does not have that restriction. Furthermore, we address inefficiencies of existing work by developing two optimized algorithms. The first only generates unique rules by preventing synthesis of duplicate and composite rules. The second only generates lowest-cost rules by preventing synthesis of higher-cost rules. We evaluate our algorithms on multiple ISAs. Without our optimizations, the vast majority of synthesized rewrite rules are either duplicates, composites, or higher cost. Our optimizations result in synthesis speed-ups of up to  $768 \times$  and  $4004 \times$  for the two algorithms.

### I. Introduction

As we approach the end of Moore's law and Dennard scaling, drastically improving computing performance and energy efficiency requires designing domain-specific hardware architectures (DSAs) or adding domain-specific extensions to existing architectures [22]. As a result, many DSAs have been developed in recent years [4], [8], [24], [27], [30], each with its own custom instruction set architecture (ISA) or ISA extension.

Targeting such ISAs from a compiler's intermediate representation (IR) requires a custom library of instruction selection rewrite rules. A rewrite rule is a mapping of an IR pattern to a functionally equivalent ISA pattern. Manual specification of rewrite rules is error-prone, time-consuming, and often incomplete. It is therefore desirable to automatically generate valid rewrite rules.

When specifying instruction selection rewrite rules, there are two common cases. When ISAs have complex instructions, rewrite rules will often map multi-instruction IR patterns to a single ISA instruction. When ISAs have simple instructions, rewrite rules will often map a single IR instruction to a multiinstruction ISA pattern. A rewrite rule generation tool should be able to create rewrite rules for both cases. We call such rewrite rules many-to-many rules.

Generating instruction selectors is not a new idea. Most relevant to this work is Gulwani et al. [21] who use a satisfiability modulo theories (SMT) solver to synthesize a loop-free program that is functionally equivalent to a given specification. Their approach is called component-based program synthesis (CBPS), as each synthesized program must include functional components from a given component library. Buchwald et al. [6] use and extend CBPS to efficiently generate multiinstruction loop-free IR programs equivalent to a single ISA instruction program; that is, they solve the many-to-one rewrite rules synthesis problem. However, multi-instruction ISA programs cannot be synthesized.

Both of these algorithms produce many duplicate rules, which are removed during a post-processing step. As we show, this adds significant additional cost. Another issue is that CBPS as currently formulated does not incorporate the notion of optimizing for cost. In practice, we often want only the set of lowest-cost rules, making it unnecessary (and expensive) to generate equivalent higher-cost rules.

This paper presents an algorithm for automatically generating a complete set of many-to-many rewrite rules. We address the above issues by preventing the synthesis of both duplicate and high-cost rules at rule generation time, using exclusion techniques. As a further optimization, we generate

rules in stages and exclude *composite* rules, i.e., rules that can be composed of smaller rules found in previous stages. These ensure we produce a small but complete set of rewrite rules. Compared to previous work, our approach eliminates unnecessary rules and significantly reduces the time required to produce the unique necessary ones.

Our contributions are as follows:

- We define generalized component-based program synthesis (GCBPS) as the task of synthesizing two functionally equivalent programs using two component libraries. We then present an SMT-based synthesis approach inspired by Gulwani et al. to solve it.

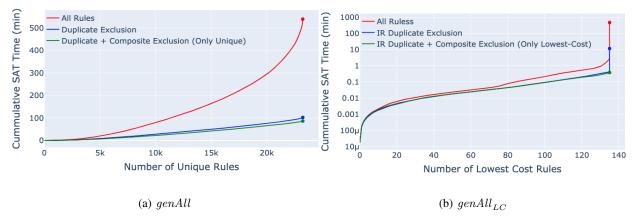

- We present an iterative algorithm *genAll* to generate all unique many-to-many rules up to a given size. We identify a set of equivalence relations for patterns encoded as programs and for rules that map IR programs to ISA programs. We use these relations to enumerate and exclude duplicate rules. Furthermore, we directly exclude composite rewrite rules. These result in up to a 768× synthesis speed-up.

- We present an algorithm  $genAll_{LC}$  which generates only the lowest-cost rules by incorporating a cost metric in addition to excluding duplicate and composite rewrite rules. This results in a synthesis speed-up up to  $4004\times$ .

The rest of the paper is organized as follows. Section II discusses instruction selection, existing rule generation methods, SMT, and program synthesis. Section III describes a program synthesis query for generating many-to-many rules. Section IV presents an algorithm for generating only unique rewrite rules and defines duplicates and composites. Section V presents an algorithm for synthesizing only the lowest-cost rules. Section VI evaluates both algorithms, and Section VII discusses limitations and further optimizations.

### II. BACKGROUND AND RELATED WORK

# A. Instruction Selection

Instruction selection is the task of translating code in the compiler's intermediate representation (IR) to functionally equivalent code for a target ISA. Typically, a library of rewrite rules is used in instruction selection. A rewrite rule is a mapping from an IR pattern consisting of IR instructions to a functionally equivalent ISA pattern consisting of ISA instructions. Such patterns can be expression trees or directed acyclic graphs (DAGs).

Significant work has been devoted to developing rewrite rule tiling algorithms to perform instruction selection [1], [5], [12], [14]–[17], [19], [26], [29]. For each rule in the rule library, a tiling algorithm first finds all fragments from the IR program in which the rule's IR pattern exactly matches that fragment. Then, the instruction selector finds a tiling of these matches that completely covers the basic block and minimizes the total rule cost according to some cost metric.

Simple instruction selectors only handle tree-based IR patterns, which is inefficient for reused computations. Modern instruction selectors like LLVM use DAG-based matching that allows for both richer rules and better tiling. Koes et al. [26] describe a similar near-optimal DAG-based instruction selection algorithm [5]. We want to generate rules that can be used with such modern DAG-based instruction selectors.

# B. Generating Instruction Selectors

Generating instruction selectors from instruction semantics has been a topic of research interest [6], [7], [9], [10], [23]. Dias and Ramsey [10] introduce an algorithm for generating rewrite rules based on a declarative specification of the ISA. While this solves part of the many-to-many rule task, their work relies on an existing set of algebraic rewrite rules for synthesizing semantically equivalent rules. Our work uses SMT for the instruction and program semantics. However, incorporating certain kinds of algebraic rewrite rules could be an avenue for future optimizations.

Daly et al. [9] propose a way to synthesize instruction selection rewrite rules from the register-transfer level (RTL) specification of a processor. Their algorithm requires a set of pre-specified IR patterns. In contrast, we can efficiently synthesize rules that consider all possible multi-instruction IR patterns up to a given size. Their approach for synthesizing complex instruction constants and handling floating point types could be combined with the approaches in this paper.

The most relevant to this work is the work by Buchwald et al. [6], which leverages component-based program synthesis to generate rules with multi-instruction IR patterns and single-instruction ISA patterns. In contrast, our work synthesizes rules with both multi-instruction IR patterns and multi-instruction ISA patterns. We additionally prevent the synthesis of duplicate, composite, and high-cost rewrite rules, unlike any of the above approaches.

# C. Program Synthesis and Equivalence

We use SMT-based program synthesis to enumerate a complete set of instruction selection rewrite rules. In program synthesis enumeration, it is common to remove equivalent solutions [3]. We use the equivalence relation defined in Section IV-A to determine equivalent rewrite rules. In prior work [2], observational equivalence (i.e., programs with the same semantics) has been used for de-duplication [2], however observational equivalence does not take into account the structure of the program, which is essential for rewrite rule pattern matching.

# D. Logical Setting and Notation

We work in the context of many-sorted logic (e.g., [13]), where we assume an infinite set of variables of each sort and the usual notions of terms, formulas, assignments, and interpretations. Terms are denoted using non-boldface symbols (e.g., X). Boldface symbols (e.g., X) are used for sets, tuples, and multisets, whose elements are either terms or other collections of terms.  $\mathbf{Y} := (Y_1, ..., Y_N)$  defines a tuple, where  $|\mathbf{Y}| = N$  and  $Y_i$  refers to the i-th element.  $\mathbf{Z} := \{z^n\}$  defines a multiset, where the multiplicity of element z is  $n \in \mathbb{N}$ . Both  $\psi$  and  $\phi$  are used to denote formulas.  $\psi(\mathbf{X})$  is a formula

whose free variables are a subset of  $\mathbf{X}$ . We use  $\mathcal{M} \vDash \psi(\mathbf{X})$  to denote the *satisfiability* relation between the interpretation  $\mathcal{M}$  and the formula  $\psi$ . Assuming  $\mathbf{X}$  is a collection of variables,  $\mathcal{M}_{\mathbf{X}}$  denotes the *assignment* to those variables induced by  $\mathcal{M}$ . For an assignment  $\alpha$ , we write  $\alpha \vDash \psi(\mathbf{X})$  if  $\mathcal{M} \vDash \psi(\mathbf{X})$  for every interpretation  $\mathcal{M}$  such that  $\mathcal{M}_{\mathbf{X}} = \alpha$ .

# E. Component-based Program Synthesis

CBPS is a program synthesis task introduced by Gulwani et al. The inputs to the task are:

- A specification  $\mathbf{S} := (\mathbf{I}^S, O^S, \phi_{spec}(\mathbf{I}^S, O^S))$  containing a tuple of input variables  $\mathbf{I}^S$ , a single output variable  $O^S$ , and a formula  $\phi_{spec}(\mathbf{I}^S, O^S)$  relating the inputs and the output.

- A library of components (e.g., instructions)  $\mathbf{K}$ , where the k-th component  $\mathbf{K}_k := (\mathbf{I}_k, O_k, \phi_k(\mathbf{I}_k, O_k))$  consists of a tuple of input variables  $\mathbf{I}_k$ , a single output variable  $O_k$ , and a formula  $\phi_k(\mathbf{I}_k, O_k)$  defining the component's semantics.

An example component for an addition instruction is shown below using the theory of bit-vectors, QF\_BV, where  $BV_{[n]}$  is an n-bit sort and  $+_{[n]}$  is addition modulo  $2^n$ .

$$((I_0:BV_{\lceil 16\rceil},I_1:BV_{\lceil 16\rceil}),O:BV_{\lceil 16\rceil},I_0+_{\lceil 16\rceil}I_1=O)$$

The task is to synthesize a valid program functionally equivalent to the specification using each component from **K** exactly once.

For notational convenience, we group together the set of all inputs and outputs of the components:  $\mathbf{W} := \cup_{(\mathbf{I}_k,O_k,\_) \in \mathbf{K}} (O_k \cup (\cup \mathbf{I}_k))$ . Gulwani et al. encode the program structure using a connection constraint:  $\phi_{conn}(\mathbf{L},\mathbf{I}^S,O^S,\mathbf{W})$ . This is a formula representing how the program inputs  $(\mathbf{I}^S)$  and program output  $(O^S)$  are connected via the components. The connections are specified using location variables  $\mathbf{L}$ . We do not go into the details of how location variables encode connections (they are in [21]). It is sufficient for our purposes to know that these are integer variables, and an assignment to them uniquely determines a way of connecting the components together into a program. The program semantics  $\phi_{prog}$  are defined as the components' semantics conjoined with the connection constraint:

$$\phi_{prog}(\mathbf{L}, \mathbf{I}^{S}, O^{S}, \mathbf{W}) := \left( \bigwedge_{k} \phi_{k}(\mathbf{I}_{k}, O_{k}) \right) \wedge \phi_{conn}(\mathbf{L}, \mathbf{I}^{S}, O^{S}, \mathbf{W}).$$

(1)

They define a verification constraint that holds if a particular program is both well-formed (specified using a well-formedness constraint  $\psi_{wfp}$ ) and satisfies the specification  $\phi_{spec}$ :

$$\phi_{verif} := \psi_{wfp}(\mathbf{L}) \wedge \forall \mathbf{I}^S, O^S, \mathbf{W}.$$

$$\phi_{prog}(\mathbf{L}, \mathbf{I}^S, O^S, \mathbf{W}) \implies \phi_{spec}(\mathbf{I}^S, O^S).$$

(2)

A synthesis formula  $\phi_{synth}$  existentially quantifies L in (2):

$$\phi_{synth} := \exists \mathbf{L}. \forall \mathbf{I}^S, O^S, \mathbf{W}.$$

$$\psi_{wfp}(\mathbf{L}) \wedge \left(\phi_{prog}(\mathbf{L}, \mathbf{I}^S, O^S, \mathbf{W}) \implies \phi_{spec}(\mathbf{I}^S, O^S)\right).$$

(3)

This formula can be solved using a technique called counter-example guided inductive synthesis (CEGIS). CEGIS solves such exist-forall formulas by iteratively solving a series of quantifier-free queries and is often more efficient than trying to solve the quantified query directly. More details are in [21]. For our purposes, we assume the existence of a CEGIS implementation, CEGIS, which takes an instance of  $\phi_{synth}$  and returns a model  $\mathcal M$  with the property that  $\mathcal M_{\mathbf L} \models \phi_{verif}$ , from which a program that is a solution to CBPS can be constructed.

# III. COMPONENT-BASED PROGRAM SYNTHESIS FOR MANY-TO-MANY RULES

Given the IR and ISA instruction sets  $\mathbf{K}^{IR}$  and  $\mathbf{K}^{ISA}$ , Buchwald et al. [6] use CBPS to synthesize rewrite rules. They use a single ISA instruction  $\mathbf{k}^{ISA} \in \mathbf{K}^{ISA}$  for the CBPS specification and a subset of the IR instructions for the CBPS components. A solution to the resulting  $\phi_{synth}$  formula gives a program  $\mathbf{P}^{IR}$ . If  $\mathbf{P}^{ISA}$  is the single-instruction program consisting of  $\mathbf{k}^{ISA}$ , they interpret the pair  $(\mathbf{P}^{IR}, \mathbf{P}^{ISA})$  as an instruction selection rewrite rule.

However, Buchwald et al.'s solution is insufficient for generating many-to-many rules, as they cannot synthesize IR and ISA programs that both contain multiple instructions. Instead, two functionally equivalent programs need to be synthesized. We first define an extension to CBPS called generalized component-based program synthesis (GCBPS) to address this problem. Then, we show how to construct a synthesis query whose solutions represent pairs of functionally equivalent programs.

# A. Generalized Component-based Program Synthesis

We define the GCBPS task as that of synthesizing two programs,  $\mathbf{P}^a$  and  $\mathbf{P}^b$ , represented using location variables  $\mathbf{L}^a$  and  $\mathbf{L}^b$ , given two sets of components  $\mathbf{K}^a$  and  $\mathbf{K}^b$ , two sets of inputs  $\mathbf{I}^a, \mathbf{I}^b$  where  $|\mathbf{I}^a| = |\mathbf{I}^b|$ , and two outputs  $O^a, O^b$  where the following conditions hold true:

- 1)  $\mathbf{P}^a$  uses each component in  $\mathbf{K}^a$  exactly once.

- 2)  $\mathbf{P}^b$  uses each component in  $\mathbf{K}^b$  exactly once.

- 3)  $\mathbf{P}^a$  is functionally equivalent to  $\mathbf{P}^b$ .

# B. Solving GCBPS

We start with the CBPS verification constraint from (2) using components  $\mathbf{K}^a$  (and a corresponding set of inputs and outputs  $\mathbf{W}^a$ ), but modify it slightly by introducing variables  $(\mathbf{I}^a, O^a)$  that are fresh copies of  $(\mathbf{I}^S, O^S)$ :

$$\psi_{wfp}(\mathbf{L}^{a}) \wedge \forall \mathbf{I}^{a}, O^{a}, \mathbf{W}^{a}, \mathbf{I}^{S}, O^{S}.$$

$$(\phi_{prog}^{a}(\mathbf{L}^{a}, \mathbf{I}^{a}, O^{a}, \mathbf{W}^{a}) \wedge \phi_{spec}(\mathbf{I}^{S}, O^{S})) \implies$$

$$((\wedge_{i} I_{i}^{a} = I_{i}^{S}) \implies O^{a} = O^{S}).$$

$$(4)$$

Assuming the formulas for both the program and the specification, if their inputs are the same, their outputs must also be the same.

We next replace the specification program with a different component-based program using components  $\mathbf{K}^b$  and quantify over that program's inputs  $\mathbf{I}^b$ , output  $O^b$ , and component variables  $\mathbf{W}^b$ :

$$\phi_{verif} := \psi_{wfp}(\mathbf{L}^{a}) \wedge \psi_{wfp}(\mathbf{L}^{b}) \wedge \forall \mathbf{I}^{a}, \mathbf{I}^{b}, O^{a}, O^{b}, \mathbf{W}^{a}, \mathbf{W}^{b}.$$

$$\left(\phi_{prog}^{a}(\mathbf{L}^{a}, \mathbf{I}^{a}, O^{a}, \mathbf{W}^{a}) \wedge \phi_{prog}^{b}(\mathbf{L}^{b}, \mathbf{I}^{b}, O^{b}, \mathbf{W}^{b})\right) \Longrightarrow$$

$$\left(\left(\wedge_{i} I_{i}^{a} = I_{i}^{b}\right) \Longrightarrow O^{a} = O^{b}\right).$$

$$(5)$$

This is our generalized verification constraint stating the correctness criteria for when two component-based programs are semantically equivalent.

To synthesize such a pair of programs, a synthesis formula  $\phi_{synth}$  is defined by existentially quantifying  $\mathbf{L}^a$  and  $\mathbf{L}^b$  in the verification formula (5):

$$\phi_{synth} := \exists \mathbf{L}^{a}, \mathbf{L}^{b}.\forall \mathbf{I}^{a}, \mathbf{I}^{b}, O^{a}, O^{b}, \mathbf{W}^{a}, \mathbf{W}^{b}.$$

$$\psi_{wfp}(\mathbf{L}^{a}) \wedge \psi_{wfp}(\mathbf{L}^{b}) \wedge$$

$$\left( \left( \phi_{prog}^{a}(\mathbf{L}^{a}, \mathbf{I}^{a}, O^{a}, \mathbf{W}^{a}) \wedge \phi_{prog}^{b}(\mathbf{L}^{b}, \mathbf{I}^{b}, O^{b}, \mathbf{W}^{b}) \right) \implies$$

$$\left( \left( \wedge_{i} I_{i}^{a} = I_{i}^{b} \right) \implies O^{a} = O^{b} \right) \right).$$

$$((\wedge_{i} I_{i}^{a} = I_{i}^{b}) \implies O^{a} = O^{b})$$

As above, we assume that calling CEGIS on  $\phi_{synth}$  returns a model  $\mathcal{M}$  such that  $\mathcal{M}_{\mathbf{L}^a \cup \mathbf{L}^b} \models \phi_{verif}$ . This can be converted into a pair of programs  $(\mathbf{P}^a, \mathbf{P}^b)$  representing a rewrite rule that is a solution for the GCBPS task. We write  $rewriteRule(\mathbf{K}^a, \mathbf{K}^b, \mathcal{M}_{\mathbf{L}^a}, \mathcal{M}_{\mathbf{L}^b})$  for the rewrite rule constructed from a specific model  $\mathcal{M}$  using the component sets  $\mathbf{K}^a$  and  $\mathbf{K}^b$ .

# IV. GENERATING ALL MANY-TO-MANY REWRITE RULES

Buchwald et al. [6] describe an iterative algorithm, *IterativeCEGIS*, to synthesize rewrite rules using CBPS. This algorithm iterates over all multisets of IR instructions up to a given size and only runs synthesis on each such multiset. Compared to running synthesis using all the IR instructions at once, this iterative algorithm works better in practice.

However, *IterativeCEGIS* cannot synthesize rewrite rules with both multi-instruction IR programs and multi-instruction ISA programs. Furthermore, it produces duplicate rewrite rules which are then filtered out in a post-synthesis filtering step. Although the results are correct, this approach is highly inefficient because each call to CEGIS is expensive, and a CEGIS call is made, not just for some duplicate rules, but for every duplicate rule. In our approach, we make the requirement that a solution is not a duplicate part of the CEGIS query itself, ensuring that each successful CEGIS query finds a new, non-redundant rewrite rule.

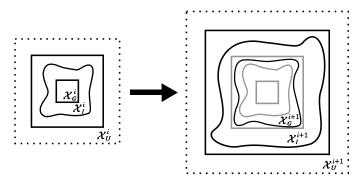

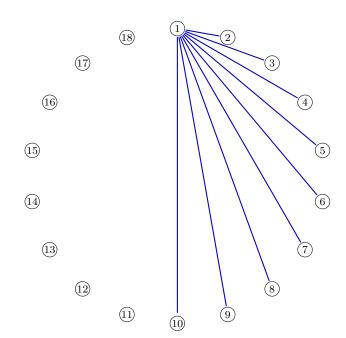

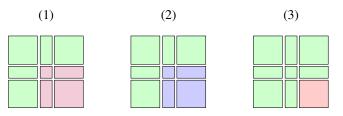

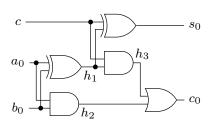

Our iterative algorithm, genAll, is shown in Figure 1. It takes as parameters the IR and ISA component sets,  $\mathbf{K}^{IR}$

```

\begin{array}{ll} 1 & genAll(\mathbf{K}^{IR}, \mathbf{K}^{ISA}, N^{IR}, N^{ISA}): \\ 2 & \mathbb{S}_R \leftarrow \{\} \\ 3 & \textbf{for } n_1, n_2 \in [1, N^{IR}] \times [1, N^{ISA}]: \\ 4 & \textbf{for } \mathbf{m}^{IR} \in multicomb(\mathbf{K}^{IR}, n_1): \\ 5 & \textbf{for } \mathbf{m}^{ISA} \in multicomb(\mathbf{K}^{ISA}, n_2): \\ 6 & \textbf{for } \mathbf{I}^{IR}, \mathbf{I}^{ISA} \in allInputs(\mathbf{m}^{IR}, \mathbf{m}^{ISA}): \\ 7 & \phi, \mathbf{L}^{IR}, \mathbf{L}^{ISA} \leftarrow \\ & GCBPS(\mathbf{m}^{IR}, \mathbf{m}^{ISA}, \mathbf{I}^{IR}, \mathbf{I}^{ISA}) \\ 8 & \phi \leftarrow \phi \wedge \neg AllComposites(\mathbb{S}_R, \ldots) \\ 9 & \mathbb{S}_R \leftarrow \mathbb{S}_R \cup \\ & CEGISAll(\phi, \mathbf{m}^{IR}, \mathbf{m}^{ISA}, \mathbf{L}^{IR}, \mathbf{L}^{ISA}) \\ 10 & \textbf{return } \mathbb{S}_R \end{array}

```

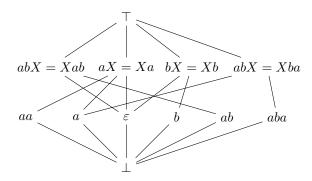

Fig. 1: Iterative algorithm to generate all unique rewrite rules up to a given size.

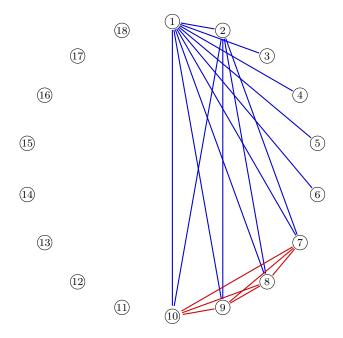

```

1 CEGISAll(\phi, \mathbf{m}^{IR}, \mathbf{m}^{ISA}, \mathbf{L}^{IR}, \mathbf{L}^{ISA}):

2 \mathbb{S}_{R} = \{\}

3 while True:

4 \mathcal{M} \leftarrow CEGIS(\phi)

5 if \mathcal{M} = \bot: return \mathbb{S}_{R}

6 \mathbf{R} \leftarrow rewriteRule(\mathbf{m}^{IR}, \mathbf{m}^{ISA}, \mathcal{M}_{\mathbf{L}^{IR}}, \mathcal{M}_{\mathbf{L}^{ISA}})

7 \mathbb{S}_{R} \leftarrow \mathbb{S}_{R} \cup \{\mathbf{R}\}

8 \phi \leftarrow \phi \land \neg \psi_{dup}(\mathbf{R}, (\mathbf{L}^{IR}, \mathbf{L}^{ISA}))

```

Fig. 2: AllSAT algorithm to synthesize all unique rules. Line 8 excludes all rules that are duplicates of the current synthesized rewrite rule.

and  $\mathbf{K}^{ISA}$  respectively, as well as a maximum number of components of each kind to use in rewrite rules,  $N^{IR}$  and  $N^{ISA}$ , and iteratively builds up a set  $\mathbb{S}_R$  of rewrite rules, which it returns at the end. Line 3 shows that  $n_1$  and  $n_2$ iterate up to these maximum sizes. Line 4 iterates over all multisets of elements from  $\mathbf{K}^{IR}$  of size  $n_1$  using a standard multicombination algorithm multicomb [25] (not shown). Line 5 is similar but for multisets from  $\mathbf{K}^{ISA}$  of size  $n_2$ . Next, for a given choice of multisets, line 6 enumerates all possible ways of selecting input vectors from those multisets that could create well-formed programs by constructing two fresh sets of input variables. Line 7 constructs fresh sets of location variables  $\mathbf{L}^{IR}$ and  $\mathbf{L}^{ISA}$  and returns them along with the instantiated GCBPS synthesis formula (using Equation (6)). Line 8 excludes all composite rules from the synthesis search space. Composite rules are rules that can be constructed using the current set of rules  $\mathbb{S}_R$  and are thus unnecessary for instruction selection. We discuss this in more detail in Section IV-B. Finally, on line 9, the current set of rules  $S_R$  is updated with the result of calling CEGISAll, which we describe next.

Figure 2 shows the CEGISAll algorithm that performs the AllSAT [20], [31] task. Its parameters are the synthesis formula  $\phi$ , the multisets  $\mathbf{m}^{IR}$  and  $\mathbf{m}^{ISA}$ , and the location variables  $\mathbf{L}^{IR}$  and  $\mathbf{L}^{ISA}$ . It returns a set  $\mathbb{S}_R$  of rewrite rules. Initially, this set is empty. The algorithm iteratively calls

<sup>&</sup>lt;sup>1</sup>We augment the well-formed program constraint in (6) to prevent synthesizing programs containing dead code and unused inputs. This can be accomplished by enforcing that each input and intermediate value is used in at least one location.

a standard CEGIS algorithm to solve the synthesis query, constructing a new rewrite rule  $\mathbf{R}$ , which is added to the set  $\mathbb{S}_R$  of rewrite rules, when the call to CEGIS is successful. The iteration repeats until the CEGIS query returns  $\bot$ , indicating that there are no more rewrite rules to be found. Note that after each iteration, the  $\phi_{synth}$  formula is refined by adding the negation of a formula capturing the notion of duplicates for this rule. We describe how this is done next.

# A. Excluding Duplicate Rules

Consider the two distinct rules below. As a syntactical convention, infix operators are used for IR patterns and function calls for ISA patterns.

$$I_1 + (I_2 \cdot I_3) \to add(I_1, mul(I_2, I_3))$$

$(I_1 \cdot I_3) + I_2 \to add(I_2, mul(I_1, I_3))$

The two IR patterns represent the same operation despite the fact that the variable names and the order of the commutative arguments to addition are both different. Both rules would match the same program fragments in an instruction selector and would result in the same rewrite rule application. Thus, we consider such rules to be equivalent and would like to ensure that only one is generated by our algorithm.

We first define a rewrite rule equivalence relation,  $\sim_{rule}$ . Informally, two rules are equivalent if replacing either one by the other has no discernible effect on the execution of an instruction selection algorithm. We make this more formal by considering various attributes of standard instruction selection algorithms.

Commutative Instructions Modern pattern matching algorithms used for instruction selection try all argument orderings for commutative instructions [5]. We define the commutative equivalence relation  $\sim_{C^{IR}}$  as  $\mathbf{P}_1^{IR} \sim_{C^{IR}} \mathbf{P}_2^{IR}$  iff  $\mathbf{P}_2^{IR}$  is a remapping of  $\mathbf{P}_1^{IR}$ 's commutative instruction's arguments.

Same-kind Instructions Programs  $\mathbf{P}$  generated by GCPBS have a unique identifier, the program line number, for each instruction. This means that if two instructions of the same kind appear in a program, interchanging their line numbers results in a different program, even though it makes no difference to the instruction selection algorithm. We define the same-kind equivalence relation  $\sim_{K^{IR}}$  as  $\mathbf{P}_1^{IR} \sim_{K^{IR}} \mathbf{P}_2^{IR}$  iff  $\mathbf{P}_2^{IR}$  is the result of remapping the line numbers for same-kind instructions in  $\mathbf{P}_1^{IR}$ .

**Data Dependency** Modern instruction selection algorithms perform pattern matching, not based on a total order of instructions, but on a partial order determined by data dependencies. Many different sequences may thus lead to the same partial order. We define  $\sim_{D^{IR}}$  as  $\mathbf{P}_1^{IR} \sim_{D^{IR}} \mathbf{P}_2^{IR}$  iff  $\mathbf{P}_1^{IR}$  and  $\mathbf{P}_2^{IR}$  have the same data dependency graph.

**Rule Input Renaming** For a given rewrite rule, the input variables used for the IR program must match the input variables used for the ISA program, but the specific variable identifiers used do not matter. We define the equivalence relation  $\sim_{I^{rule}}$  on rules (i.e., pairs of programs) as  $\mathbf{R}_1 \sim_{I^{rule}} \mathbf{R}_2$  iff  $\mathbf{R}_2$  is the result of remapping variable identifiers in  $\mathbf{R}_1$ .

**Rule Equivalence** The first three equivalence relations defined above are for IR programs, but the analogous relations ( $\sim_{C^{ISA}}$ ,  $\sim_{K^{ISA}}$ ,  $\sim_{D^{ISA}}$ ) for ISA instructions are also useful.

Putting everything together, we define rule equivalence  $\sim_{rule}$  as follows.

$$\sim_{IR} := \uplus \{\sim_{C^{IR}}, \sim_{K^{IR}}, \sim_{D^{IR}}\}$$

(7)

$$\sim_{ISA} := \uplus \{\sim_{C^{ISA}}, \sim_{K^{ISA}}, \sim_{D^{ISA}}\}$$

(8)

$$\sim_{rule} := \uplus \{ (\sim_{IR} \otimes \sim_{ISA}), \sim_{I^{rule}} \}$$

(9)

Overall IR equivalence is defined as the transitive closure of the union (notated with  $\uplus$ ) of the three individual IR relations. ISA equivalence is defined similarly. Overall rewrite rule equivalence is then defined using the  $\otimes$  operator, where  $\sim_{\otimes}=\sim_{a}\otimes\sim_{b}$  is defined as:  $(a_{1},b_{2})\sim_{\otimes}(a_{2},b_{2})$  iff  $a_{1}\sim_{a}a_{2}$  and  $b_{1}\sim_{b}b_{2}$ . Specifically, rule equivalence is obtained by combining IR equivalence in this way with ISA equivalence, and then combining the result with  $\sim_{Irule}$  using  $\uplus$ .

The set of all duplicates of rule  $\mathbf{R}$  is the rule equivalence class  $[\mathbf{R}]_{rule}$ , where  $\mathbf{R}' \in [\mathbf{R}]_{rule} \iff \mathbf{R} \sim_{rule} \mathbf{R}'$ .  $\psi_{dup}$  can be constructed as the disjunction of all elements of the equivalence class  $[\mathbf{R}]_{rule}$

# B. Excluding Composite Rules

We also exclude any rule whose effect can already be achieved using the current set of generated rules (line 8 of Figure 1). We elucidate this using a simple example. Assume the algorithm just constructed a new query for the multisets  $\mathbf{m}^{IR}$ ,  $\mathbf{m}^{ISA}$ , and the input  $\mathbf{I}^{IR}$  (line 7 of Figure 1), and assume that the rule library  $\mathbb{S}_R$  currently contains rules for addition  $(I_1 + I_2 \rightarrow add(I_1, I_2))$  and multiplication  $(I_1 \cdot I_2 \rightarrow mul(I_1, I_2))$ . Consider the following cases.

- 1) If  $\mathbf{I}^{IR} = (I_1)$ ,  $\mathbf{m}^{IR} = \{+\}$ , and  $\mathbf{m}^{ISA} = \{add\}$ , then the rule  $I_1 + I_1 \rightarrow add(I_1, I_1)$  will be synthesized by *CEGISAll*. But this rule is a *specialization* of the existing rule for addition. Any use of this specialized rule could instead be replaced by the more general rule, and this rule can thus be excluded. Note that we order the inputs on line 6 of Figure 1 to guarantee that the most general version of a rule is found first.

- 2) If I<sup>IR</sup> = (I<sub>1</sub>, I<sub>2</sub>, I<sub>3</sub>), m<sup>IR</sup> = {+,·}, and m<sup>ISA</sup> = {add, mul}, then the composite rule (I<sub>1</sub> + (I<sub>2</sub> · I<sub>3</sub>)) → add(I<sub>1</sub>, mul(I<sub>2</sub>, I<sub>3</sub>)) will be synthesized by CEGISAll. Using similar logic, any use of this composite rule could instead use the simpler and more general rules for addition and multiplication, and this rule can thus be excluded. The multiset ordering used in lines 4 and 5 of Figure 1 ensures that subsets are visited before supersets, guaranteeing that smaller rules are found first. A specialized rule can be interpreted as a composite rule composed of the general rule with fewer inputs.

Only composite rules that would have been synthesized for a particular query need to be excluded. In general, for a specific query based on  $\mathbf{m}^{IR}$ ,  $\mathbf{m}^{ISA}$ , and  $\mathbf{I}^{IR}$ , we enumerate and exclude composite rules  $\mathbf{R} := (\mathbf{P}^{IR}, \mathbf{P}^{ISA})$  that meet the following criteria:

```

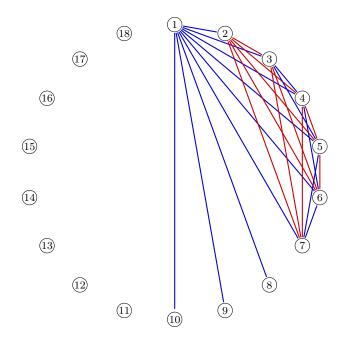

genAll_{LC}(\mathbf{K}^{IR}, \mathbf{K}^{ISA}, N^{IR}, N^{ISA}, cost):

\mathbf{K}_{sorted} \leftarrow sortByCost(\mathbf{K}^{ISA}, N^{ISA}, cost)

2

3

for \mathbf{n} \in [1, N^{IR}]:

4

for \mathbf{m}^{IR} \in multicomb(\mathbf{K}^{IR}, n):

5

for \mathbf{m}^{ISA} \in \mathbf{K}_{sorted}:

6

c_{cur} \leftarrow cost(\mathbf{m}^{ISA})

for \mathbf{I}^{IR}, \mathbf{I}^{ISA} \in allInputs(\mathbf{m}^{IR}, \mathbf{m}^{ISA}):

7

8

\phi, \mathbf{L}^{IR'}, \mathbf{L}^{ISA} \leftarrow

9

GCBPS(\mathbf{m}^{IR}, \mathbf{m}^{ISA}, \mathbf{I}^{IR}, \mathbf{I}^{ISA})

\phi \leftarrow \phi \land \neg AllComposites_{LC}(\mathbb{S}_R, c_{cur}, \ldots)

10

\mathbb{S}_R \leftarrow \mathbb{S}_R \cup

11

CEGISAll_{LC}(\phi, \mathbf{m}^{IR}, \mathbf{m}^{ISA}, \mathbf{L}^{IR}, \mathbf{L}^{ISA})

return S_R

12

```

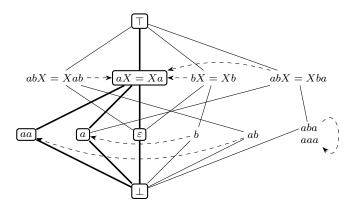

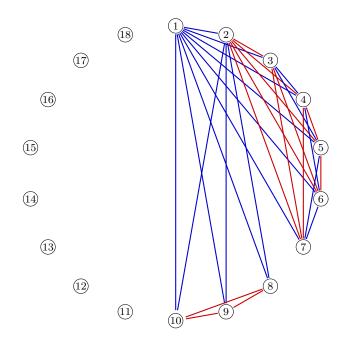

Fig. 3: Iterative algorithm to generate all lowest-cost rules. ISA multisets are ordered by cost. *CEGISAll* is modified to exclude rules with duplicate IR programs.

- $\mathbf{R}$  has exactly  $|\mathbf{I}^{IR}|$  inputs.

- ${\bf P}^{IR}$  has the same components as  ${\bf m}^{IR}$ .

- $\mathbf{P}^{ISA}$  has the same components as  $\mathbf{m}^{ISA}$ .

- $\mathbf{P}^{IR}$  is built from the IR programs of already-found rules in  $\mathbb{S}_{R}$ .

- $\mathbf{P}^{ISA}$  is the result of applying the rewrite rules used to build  $\mathbf{P}^{IR}$ .

This enumeration is encapsulated by the call to *AllComposites* on line 8 of Figure 1.

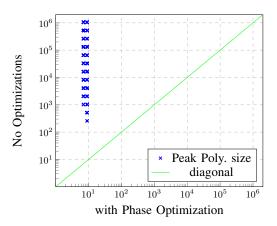

# V. GENERATING ALL LOWEST-COST RULES

Because all duplicates are excluded, the genAll algorithm generates only unique rewrite rules. However, two unique rules can share the same IR pattern. For a particular IR pattern, only the lowest-cost rule is needed for some cost metric. Knowing the instruction selection cost metric at rule-generation time presents another time-saving opportunity because we can also prevent the synthesis of high-cost rules.

We make a few assumptions about such a cost metric.

- The cost for an instruction selection tiling is equal to the sum of the costs of each tiling rule's ISA program.

- The cost of an ISA program  $\mathbf{P}^{ISA}$  only depends on the instruction *contents*, not the program structure. This cost is the sum of the cost of each instruction in the program.

While these assumptions are a restriction on the space of possible cost metrics, they are sufficient to represent common ones like code size and energy. If the compiler's cost metric violates these assumptions, the genAll algorithm can be used instead. This restricted space of cost metrics has the important property that the cost of any rule that would be synthesized using the components  $\mathbf{m}^{ISA}$  can be determined up front as the sum of the cost of each component.

Figure 3 shows our synthesis algorithm updated to only synthesize the lowest-cost rules for each unique IR pattern. The first change is to sort all possible mulitsets of ISA instructions up to size  $N^{ISA}$  by cost (lower cost first) (line 2). This ordering ensures that the first rule synthesized for a

particular IR program will be the lowest-cost version of that rule. Therefore, after synthesizing a new rule, all rules with a duplicate IR program can be excluded. The second change excludes rules with duplicate IR programs. A duplicate IR program is defined using the IR equivalence relation:

$$\sim_{IR_{LC}} := \uplus \{\sim_{C^{IR}}, \sim_{K^{IR}}, \sim_{D^{IR}}, \sim_{I^{IR}}\}$$

(10)

This is the same definition as (7), but with an additional relation  $\sim_{I^{IR}}$  defined as  $\mathbf{P}_1^{IR} \sim_{I^{IR}} \mathbf{P}_2^{IR}$  iff  $\mathbf{P}_2^{IR}$  is the result of remapping variable identifiers in  $\mathbf{P}_1^{IR}$ . The  $CEGISAll_{LC}$  function called on line 11 is the same as CEGISAll, except that it uses  $\sim_{IR_{LC}}$  instead of  $\sim_{IR}$  when constructing  $\psi_{dup}$ .

The third change modifies AllComposites to use the known up-front cost  $cost(\mathbf{m}^{ISA})$ . To see how this works, we consider again the example from Section IV-B. As before, we assume  $\mathbb{S}_R$  currently contains two rules: one for addition  $(I_1+I_2\to add(I_1,I_2))$  and one for multiplication  $(I_1\cdot I_2\to mul(I_1,I_2))$ . We assume the target (ISA) expressions for these rules have cost 5 and 10, respectively. Consider the following situation:

• Suppose  $\mathbf{I}^{IR}=(I_1,I_2,I_3)$ , and  $\mathbf{m}^{IR}=\{+,\cdot\}$ . It might be possible to synthesize a rule that has IR pattern  $(I_1+(I_2\cdot I_3))$ . We know that the composite rule  $(I_1+(I_2\cdot I_3))\to add(I_1,mul(I_2,I_3))$  would have a cost of 15 since rule costs are additive. Therefore, we can exclude any rule that matches this IR pattern and has  $cost(\mathbf{m}^{ISA})\geq 15$ .

To implement this, only one adjustment needs to be made to the conditions in Section IV-B. Instead of requiring  $\mathbf{P}^{ISA}$  to have the same components as  $\mathbf{m}^{ISA}$ , we simply require  $cost(\mathbf{P}^{ISA}) \geq cost(\mathbf{m}^{ISA})$ , i.e., for rules matching the other conditions, if the ISA program has a cost equal to or greater than cost of the ISA program in the current rule, it is excluded. These conditions are encapsulated by the call to  $AllComposites_{LC}$  (line 10).

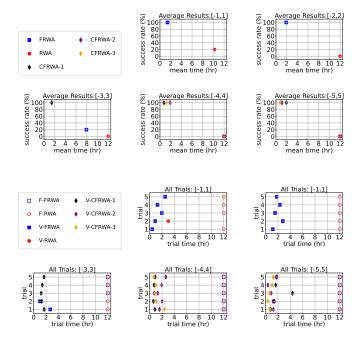

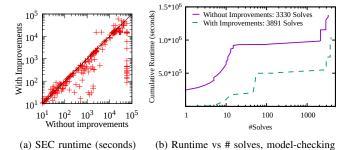

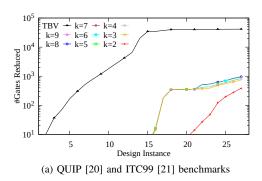

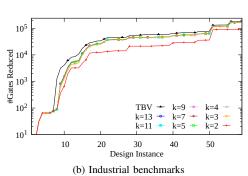

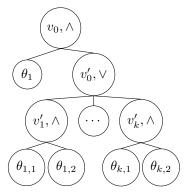

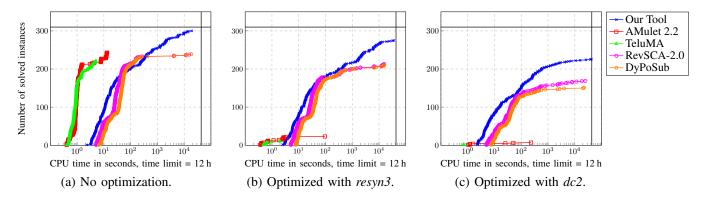

# VI. EVALUATION

Our evaluation strategy is threefold. We first show that our algorithm is capable of producing a variety of many-to-many rules. A good set of rewrite rules involves both many-to-one and one-to-many rules. We also show that by removing duplicate, composite, and high-cost rules, we produce a much smaller set of rewrite rules. Second, we analyze the effect on performance of the optimizations described above. We show that they all significantly reduce the time spent in synthesis. Finally, we show that by using different cost metrics, we can generate different sets of lowest-cost rewrite rules.

# A. Implementation

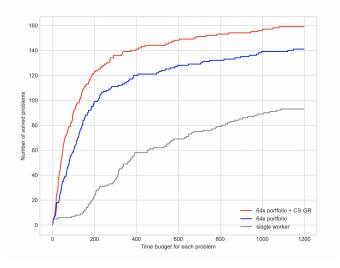

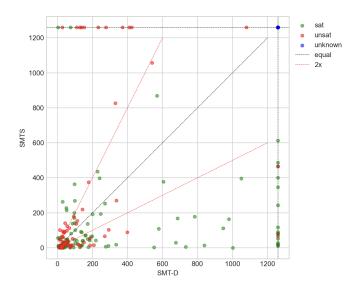

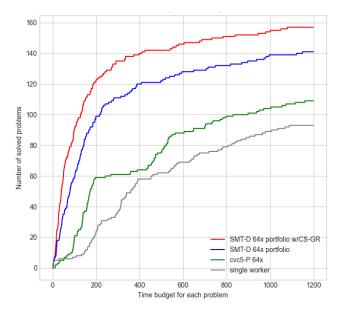

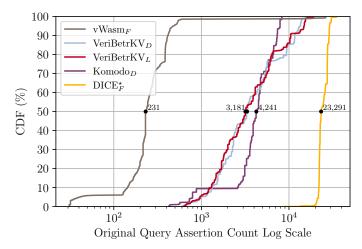

All instructions are formally specified using the hwtypes Python library [11], which leverages pySMT [18] to construct (quantifier-free) SMT queries in the theory of bit-vectors. We also use annotations indicating which instructions are commutative. We use Boolector [28] as the SMT solver and set a timeout of 12 seconds for each CEGIS invocation. Every synthesized rewrite rule is independently verified to be valid.