Ygor Quadros de Aguiar Frédéric Wrobel Jean-Luc Autran Rubén García Alía

# Single-Event Effects, from Space to Accelerator Environments

Analysis, Prediction and Hardening by Design

Single-Event Effects, from Space to Accelerator Environments

Ygor Quadros de Aguiar • Frédéric Wrobel • Jean-Luc Autran • Rubén García Alía

# Single-Event Effects, from Space to Accelerator Environments

Analysis, Prediction and Hardening by Design

Ygor Quadros de Aguiar European Organization for Nuclear Research (CERN) Geneva, Switzerland

Jean-Luc Autran University of Rennes Rennes, France Frédéric Wrobel University of Montpellier Montpellier, France

Rubén García Alía CERN–European Organization for Nuclear Research (CERN) Geneva, Switzerland

ISBN 978-3-031-71722-2 ISBN 978-3-031-71723-9 (eBook) https://doi.org/10.1007/978-3-031-71723-9

This work was supported by CERN

© The Editor(s) (if applicable) and The Author(s) 2025. This book is an open access publication.

**Open Access** This book is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this book are included in the book's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the book's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, expressed or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

If disposing of this product, please recycle the paper.

## Preface

As humanity pushes the boundaries of exploration and technology, the need to understand and mitigate the effects of radiation on electronic components in harsh environments, such as space missions and particle accelerators, has never been more critical. This book addresses that need by providing a thorough examination of radiation-induced failure mechanisms, with a particular focus on Single-Event Effects (SEEs) that pose significant challenges to the reliability of modern electronics, and how to mitigate them at the design level.

For newcomers to this field, this book offers a solid foundation in the fundamental concepts of particle interaction physics and electronics hardening design. We begin with the basics-the composition and dynamics of radiation environments and their impact on electronic components. From there, we explore the principles of component qualification and the design techniques used to harden electronics against radiation-induced failures. These sections are designed to equip new researchers and engineers with the knowledge they need to navigate this complex field.

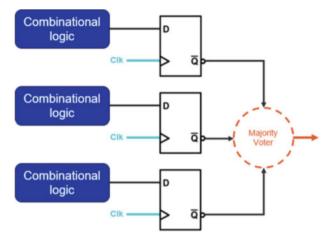

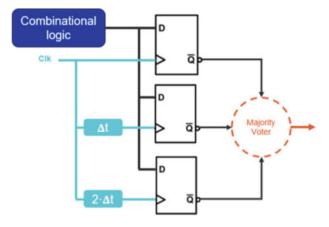

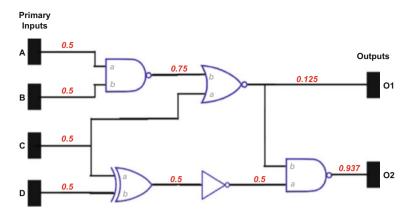

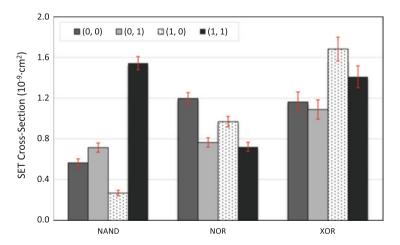

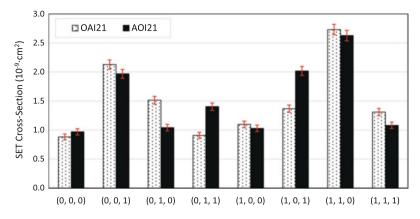

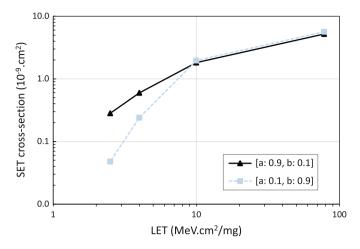

For more experienced readers, this book provides a comprehensive discussion of the state-of-the-art methodologies in modeling and advanced Radiation-Hardeningby-Design (RHBD) techniques that can be employed at both the physical layout and circuit levels. The layout design of integrated circuits plays a significant role in influencing SEE generation, and thus, layout-level hardening techniques are critical for minimizing radiation-induced charge collection. At the circuit level, this book explores the implications of logic synthesis in cell-based designs, proposing signal probability as a novel, application-specific approach to hardening. This method promises to enhance the efficiency of RHBD techniques while minimizing design drawbacks and avoiding misleading qualifications.

One of the key insights presented in this book is the potential for optimization in RHBD techniques. For instance, optimizing pin assignment to target transient effects can reduce the overall failure rate without increasing the design area. Similarly, selective Triple-Modular Redundancy (TMR) block insertion methodologies can be refined based on the signal probability of critical nodes and the robustness of majority voter architectures, leading to more efficient and reliable designs. This book is the culmination of the extensive research carried out during my PhD thesis, developed under the RADSAGA Marie Curie fellowship. It has been a privilege to contribute to this rapidly evolving field alongside esteemed colleagues and mentors, whose expertise and guidance have been invaluable. I hope that this work will serve as a useful resource for those seeking to understand and mitigate the challenges posed by radiation-induced failures in electronic components.

Finally, I would like to express my deepest gratitude to my co-authors-Professors Frédéric Wrobel, Jean-Luc Autran, and Dr. Rubén García Alía-whose contributions and insights have significantly enriched this book. Their dedication to advancing our understanding of radiation effects in electronics is truly inspiring, and I am honored to have collaborated with such distinguished experts in the field.

Geneva, Switzerland 08/2024

Ygor Quadros de Aguiar

## Acknowledgments

I am deeply grateful to my parents for their support throughout my journey from college to this moment. Without their love, encouragement, and sacrifices, I wouldn't be where I am today. I also extend my heartfelt gratitude to my twin brother and little sister for their unwavering support and encouragement.

Additionally, I wish to extend my appreciation to my colleagues from the RADIAC team at the Université de Montpellier for their friendship and support during my PhD journey. Special appreciation goes to my esteemed colleagues from the Radiation to Electronics (R2E) project at European Organization for Nuclear Research (CERN). Working alongside them has been a privilege, and I am grateful for the opportunities to collaborate and learn from each of them. In particular, I would like to express my sincere thanks to Matteo Ferrari, Samuel Niang, and Kacper Bilko for their friendship, numerous hours of conversations, and the several coffee breaks we shared together.

I owe a debt of gratitude to my supervisors and co-authors, Frédéric Wrobel, Jean-Luc Autran, and Rubén García Alía, for their unwavering support, belief in my potential, and invaluable mentorship over the past few years. Last but not least, I am thankful to God for granting me the strength and courage to pursue my dreams.

# Contents

| 1 | Rad  | tion Environment and Their Effects on Electronics | 1  |  |  |  |

|---|------|---------------------------------------------------|----|--|--|--|

|   | 1.1  | ntroduction                                       | 1  |  |  |  |

|   | 1.2  | Radiation Environments                            | 1  |  |  |  |

|   |      | .2.1 Space Environment                            | 1  |  |  |  |

|   |      | .2.2 Atmospheric Environment                      | 6  |  |  |  |

|   |      | .2.3 Accelerator Environment                      | 8  |  |  |  |

|   | 1.3  | Particle Interaction Mechanisms 1                 | 12 |  |  |  |

|   | 1.4  | Energy Deposition 1                               | 15 |  |  |  |

|   | 1.5  | Charge Collection   2                             | 21 |  |  |  |

|   |      | .5.1 Charge Sharing and Pulse Quenching Effect 2  | 23 |  |  |  |

|   | 1.6  | Summary 2                                         | 24 |  |  |  |

|   | Refe | nces 2                                            | 26 |  |  |  |

| 2 | Intr | luction to Single-Event Effects                   | 29 |  |  |  |

|   | 2.1  |                                                   | 29 |  |  |  |

|   | 2.2  |                                                   | 31 |  |  |  |

|   | 2.3  |                                                   | 35 |  |  |  |

|   | 2.4  |                                                   |    |  |  |  |

|   |      |                                                   | 38 |  |  |  |

|   |      | 2.4.2 Electrical Masking Effect                   | 38 |  |  |  |

|   |      |                                                   | 39 |  |  |  |

|   | 2.5  | Single-Event Latchup (SEL) 4                      | 10 |  |  |  |

|   | 2.6  | Summary 4                                         | 13 |  |  |  |

|   | Refe | nces                                              | 14 |  |  |  |

| 3 | Sing | -Event Effect Prediction Methodologies 4          | 19 |  |  |  |

|   | 3.1  |                                                   | 19 |  |  |  |

|   | 3.2  |                                                   | 50 |  |  |  |

|   |      |                                                   | 50 |  |  |  |

|   |      | 2.2 Drift-Diffusion-Collection Criterion          | 52 |  |  |  |

|    | 3.3  | Modeling Radiation-Induced Currents in Circuit Simulations          |     |  |  |  |

|----|------|---------------------------------------------------------------------|-----|--|--|--|

|    | 3.4  | Proposed Prediction Methodology Based on the Diffusion Model        | 55  |  |  |  |

|    | 3.5  | Summary                                                             | 58  |  |  |  |

|    | Refe | erences                                                             | 59  |  |  |  |

| 4  | Rad  | iation Hardening                                                    | 63  |  |  |  |

|    | 4.1  | Introduction                                                        | 63  |  |  |  |

|    | 4.2  | Radiation Hardening by Process (RHBP)                               | 65  |  |  |  |

|    | 4.3  | Radiation Hardening by Design (RHBD)                                | 68  |  |  |  |

|    |      | 4.3.1 Layout-Based Techniques                                       | 68  |  |  |  |

|    |      | 4.3.2 Circuit-Based Techniques                                      | 72  |  |  |  |

|    | 4.4  | Summary                                                             | 76  |  |  |  |

|    | Refe | erences                                                             | 77  |  |  |  |

| 5  | Ana  | lysis of Layout-Based RHBD Techniques                               | 81  |  |  |  |

|    | 5.1  | Introduction                                                        | 81  |  |  |  |

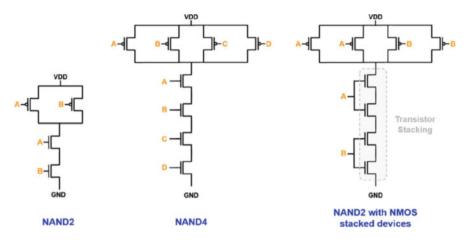

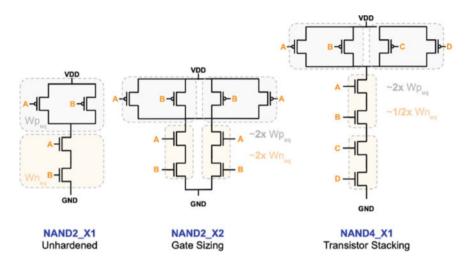

|    | 5.2  | Part I—Gate Sizing and Transistor Stacking                          | 82  |  |  |  |

|    | 5.2  | 5.2.1 Gate Sizing (GS)                                              | 82  |  |  |  |

|    |      | 5.2.1     Gate Sizing (GS)       5.2.2     Transistor Stacking (TS) | 86  |  |  |  |

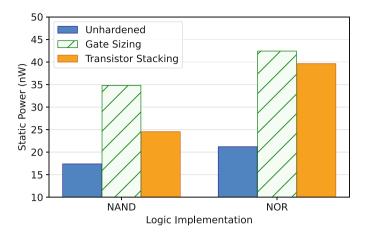

|    |      | 5.2.3 Comparison of Power and Area Overhead                         | 88  |  |  |  |

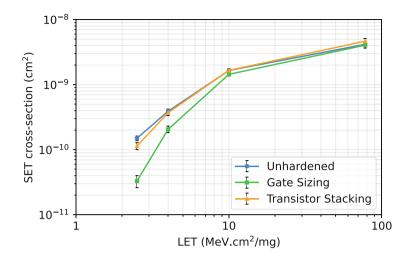

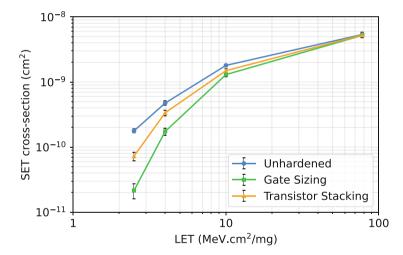

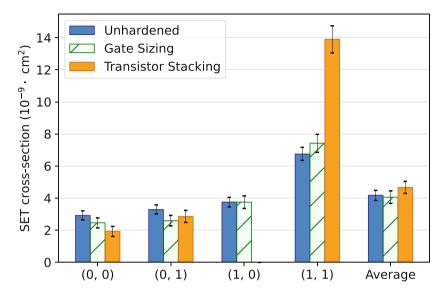

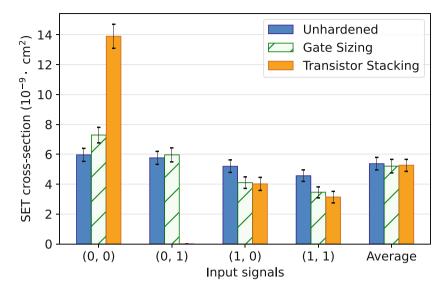

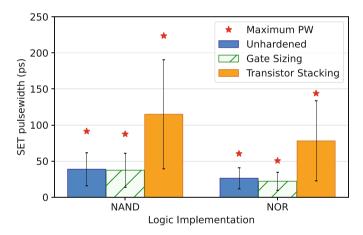

|    |      | 5.2.4 Impact on the SET Cross Section                               | 89  |  |  |  |

|    | 5.3  | Part II—Transistor Folding (TF) and Diffusion Splitting (DS)        | 94  |  |  |  |

|    | 0.0  | 5.3.1 Impact on the SET Cross Section                               | 97  |  |  |  |

|    |      | 5.3.2 Asymmetric Designs                                            | 101 |  |  |  |

|    |      | 5.3.3 Voltage Variability                                           | 104 |  |  |  |

|    |      | 5.3.4 Impact on the In-Orbit SET Rate: LEO and ISS Orbits           | 106 |  |  |  |

|    |      | 5.3.5 Transistor Scaling and Angular Dependence                     | 107 |  |  |  |

|    | 5.4  | Summary                                                             | 108 |  |  |  |

|    | Refe | erences                                                             | 110 |  |  |  |

| 6  | Ana  | lysis of Circuit-Based RHBD Techniques                              | 115 |  |  |  |

|    | 6.1  | Reliability-Driven Synthesis                                        | 115 |  |  |  |

|    |      | 6.1.1 Multiple $V_{th}$ Cells and Voltage Scaling                   | 118 |  |  |  |

|    |      | 6.1.2 Technology Mapping                                            | 120 |  |  |  |

|    | 6.2  | Pin Assignment                                                      | 125 |  |  |  |

|    |      | 6.2.1 Optimization of Pin Assignment for Single-Event               |     |  |  |  |

|    |      | Transients                                                          | 125 |  |  |  |

|    |      | 6.2.2 Impact on the SET Cross Section of Standard Cells             | 129 |  |  |  |

|    | 6.3  | Summary                                                             | 133 |  |  |  |

|    | Refe | erences                                                             | 134 |  |  |  |

|    |      |                                                                     |     |  |  |  |

| In | dex  |                                                                     | 139 |  |  |  |

# **Chapter 1 Radiation Environment and Their Effects on Electronics**

#### 1.1 Introduction

From the terrestrial landscapes of Earth to the celestial expanses of our solar system, ionizing radiation is omnipresent. It shapes the world around us, playing an indispensable role in sustaining life on Earth while also posing potential threats. Radiation itself is a form of energy emitted by atoms, taking the form of either electromagnetic waves or energetic particles. Different types of radiation interact with matter in unique ways, and they can be generated naturally, as in the case of galactic cosmic rays, or artificially, as in particle accelerators. Furthermore, the intensity and their energy vary significantly across environments. Therefore, understanding the sources and characteristics of radiation within a specific environment is crucial for ensuring safety and the effective operation of electronic systems in any given environment.

#### **1.2 Radiation Environments**

#### 1.2.1 Space Environment

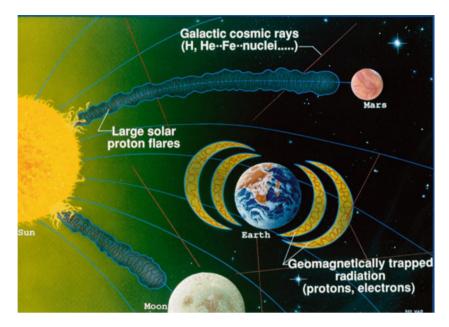

Mission success in the near-Earth space environment hinges on a thorough understanding of the prevalent radiation sources (as illustrated in Fig. 1.1). These sources can be broadly categorized into three primary types:

Solar Energetic Particles (SEPs): continuously emitted by the Sun during periods of enhanced activity, SEPs are energetic protons and heavier ions accelerated by solar flares and coronal mass ejections (CMEs). The intensity and energy spectrum of SEPs vary significantly depending on the specific solar event.

Fig. 1.1 A schematic diagram illustrating the three primary sources of radiation in near-Earth space (Adapted from [1])

- Galactic Cosmic Rays (GCRs): originating from outside our solar system, GCRs are high-energy particles, primarily consisting of protons and heavier nuclei, believed to be produced by violent events such as supernovae explosions. Due to their high energy, GCRs can penetrate deep into spacecraft and pose significant health risks to astronauts on long-duration missions. GCRs are a constant source of radiation in near-Earth space, but their flux is modulated by the Sun's heliosphere, a vast bubble of charged particles extending outward from the Sun.

- Geomagnetically Trapped Particle Radiation (Van Allen Belts): this region consists of a complex mixture of energetic particles, primarily protons and electrons, trapped by the Earth's magnetosphere. The magnetosphere is a vast, dynamic region shaped by the Earth's magnetic field, which acts as a shield against incoming charged particles from the Sun and beyond. These trapped particles form two distinct toroidal regions known as the Van Allen radiation belts. The inner belt primarily consists of high-energy protons, while the outer belt contains a broader mix of protons and electrons. The specific location and intensity of trapped particles within these belts vary depending on space weather conditions.

Solar activity plays a crucial role in shaping the near-Earth space radiation environment. Solar flares and CMEs can significantly enhance the flux of SEPs, potentially creating intense radiation bursts that can overwhelm spacecraft shielding. Furthermore, solar activity can also indirectly influence the intensity of GCRs and trapped radiation. During periods of high solar activity, the Earth's magneto-sphere becomes more compressed, allowing a higher flux of GCRs to penetrate into the inner regions near-Earth space. Additionally, energetic solar wind particles can interact with the magnetosphere, leading to enhanced particle populations within the Van Allen belts.

Therefore, understanding and monitoring solar activity through observations of sunspots and other solar phenomena is critical for predicting the radiation environment that spacecraft and sensitive electronics may encounter in near-Earth space.

**Particle flux** is the rate of particle that passes through a unit area per unit time, expressed in  $\text{cm}^{-2} \cdot \text{s}^{-1}$ , also known as *flux density*. Another widely used quantity is the **particle fluence**, which is the particle flux integrated over a period of time and expressed in cm<sup>-2</sup>.

Numerous space missions have been specifically designed to measure and comprehend solar activity, recognizing its significance for life on Earth and its influence on mission planning and design. A notable example is the Solar and Heliospheric Observatory (SOHO), a joint mission between the European Space Agency (ESA) and NASA, which was launched in 1995 and continues to operate successfully.

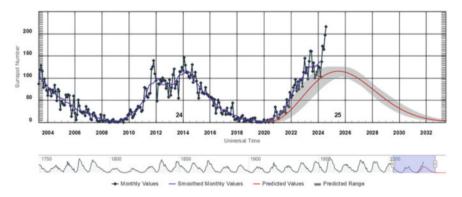

The Sun's activity follows an approximate 11-year cycle, characterized by periods of high (solar maximum, about 7 years) and low (solar minimum, about 4 years) activity. Figure 1.2 presents solar activity measurements and predictions for the upcoming cycles based on the sunspot number, also known as the *Wolf number*.

Fig. 1.2 Solar Cycle Sunspot Number Progression. The peak of cycle 25 is expected in 2025 [4]

Sunspots are cooler, darker regions on the Sun's surface associated with intense magnetic activity.

While the Sun continuously emits a low-energy stream of particles known as the solar wind, primarily consisting of protons and electrons with some heavier ions, significant radiation events are associated with solar flares and coronal mass ejections (CMEs). These infrequent but powerful events release a substantial number of highly energetic particles into space. Solar wind particles typically have energies ranging from kiloelectronvolts (keV) to gigaelectronvolts (GeV) and can reach speeds up to 80% of the speed of light.

Highly energetic particles originating from intense solar activities are particularly concerning due to their ability to rapidly reach Earth's atmosphere within hours or days. These energetic particles pose a dual threat: endangering astronauts and disrupting electronic systems in space [2]. The intensity of the solar wind and the frequency of solar particle events are directly influenced by solar activity, specifically the number of sunspots. During the solar maximum, particularly the declining phase, CMEs and solar flares occur more frequently [3].

Interestingly, solar activity has an inverse correlation with the flux of galactic cosmic rays (GCRs). GCRs are high-energy particles originating from outside the solar system and have the lowest particle flux among the radiation sources in near-Earth space. However, due to their high energy, they are highly penetrating and pose a significant threat to space-borne electronics and human health. Shielding technology offers limited protection against GCR radiation exposure.

During periods of high solar activity, the Sun's magnetic field strengthens, acting as a more effective shield against incoming particles from beyond the solar system. This leads to a decrease in the flux of GCRs reaching Earth's vicinity [5–7]. Conversely, during solar minimum periods, the weakened solar magnetic field allows a higher GCR flux to penetrate into near-Earth space. Understanding and monitoring solar activity and its associated radiation environment is crucial for several reasons:

- **Space Mission Planning:** knowledge of the radiation environment allows engineers to design spacecraft with appropriate shielding strategies and operational procedures to ensure the safety and functionality of spacecraft systems.

- Astronaut Safety: astronauts on long-duration missions are exposed to elevated levels of radiation, posing potential health risks. Understanding the radiation environment helps to develop strategies for mitigating these risks.

- Space Weather Forecasting: missions like SOHO provide valuable data that contributes to improved space weather forecasting and radiation risk assessment.

Solar events, such as solar storms and CMEs, have been documented for centuries. The *Carrington event* of 1859 serves as a powerful historical example. This massive solar storm caused significant disruptions to early telegraph systems and produced auroras visible across the globe [8, 9]. It was one of the first instances where the consequences of a solar event affecting Earth were recognized. One event in this level could be very catastrophic nowadays as modern technology is completely dependent on electricity. A more recent example occurred in January

2022, where a significant solar storm originating from a CME caused unexpected impacts on orbiting satellites [10, 11]. The solar energy from the CME increased atmospheric drag, pulling several satellites out of their intended orbits. This incident, unfortunately resulting in the loss of multiple satellites, underscores the importance of considering solar activity's potential effects when designing space missions.

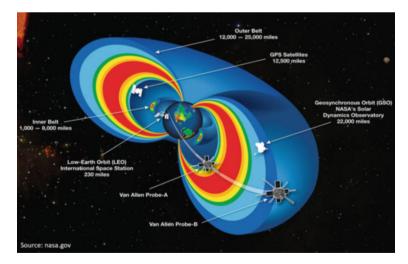

The third radiation component in the near-Earth environment is the trapped particle radiation in the Van Allen radiation belts, illustrated in Fig. 1.3. As can be seen in Fig. 1.3, the outer belt is wider than the inner belt, and it is also the most unstable due to the weaker influence of the Earth's magnetosphere. Similar to the GCRs, the trapped radiation suffers influence from the solar activity, and it is modulated such that the higher the activity, the higher is the electron flux and the lower the proton flux and vice versa [12]. Van Allen radiation belts have been always a concern for space mission designs due to their impact on electronic reliability. Protons are able to induce a variety of effects ranging from parametric degradation due to absorbed dose to even singular effects.

These radiation effects are further detailed in the next section. The analysis of the proton flux in the inner belt is highly important for any space mission targeting low-Earth orbit (LEO) as, for example, several Earth observation instruments and the International Space Station (ISS) shown in Fig. 1.3. Overall, a comprehensive understanding of the dynamics and composition of the trapped radiation belts plays a crucial role in developing effective measures to safeguard satellites against the adverse impacts of space weather.

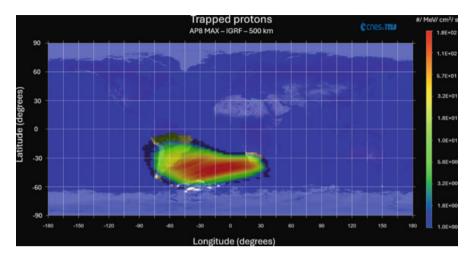

Another crucial consideration in the design of spaceborne components is the anomaly within the Earth's magnetosphere, known as the *South Atlantic Anomaly*

Fig. 1.3 Van Allen Radiation Belts [1]. The outer belt is predominantly composed of electrons, while the inner belt is predominantly composed of protons

Fig. 1.4 Flux intensity map for the >10 MeV channel at 500 km altitude. Higher proton flux in the South Atlantic Anomaly (SAA) region. The graph was obtained using the AP8 model available in the OMERE software tool [13]

(SAA). This anomaly arises from a slight tilt and offset between the Earth's geomagnetic and rotational axes, causing a significant weakening of the Earth's magnetic field over the South Atlantic region. This weakened field allows energetic particles from the Van Allen belts and galactic cosmic rays (GCRs) to penetrate lower altitudes than they typically would elsewhere, resulting in a zone of increased radiation exposure. Figure 1.4 illustrates this phenomenon, showing the AP8 MIN model's depiction of high-flux protons reaching altitudes as low as 500 km and below in the SAA region.

The presence of the SAA poses a significant challenge for spacecraft operating in LEO. The intense radiation environment within the SAA can potentially damage sensitive electronics onboard satellites. As a result, many satellites employ a precautionary measure of switching off sensitive electronic components when traversing the SAA to avoid potential damage, particularly from stochastic events (discussed in the next chapter).

#### 1.2.2 Atmospheric Environment

When cosmic rays enter the Earth's atmosphere, they interact with atmospheric atoms, primarily nitrogen and oxygen molecules, leading to the production of secondary radiation. Similarly, these secondary particles can also interact with atmospheric atoms, creating a cascade effect and generating additional secondary particles. This phenomenon is known as a *cosmic ray air shower*, and it is illustrated in Fig. 1.5. In this example, the primary cosmic particle is a highly energetic proton

Fig. 1.5 Secondary radiation induced by a high-energetic proton interacting with an atmospheric atom, nitrogen  $({}^{14}N)$ , and leading to a cascade of secondary interactions. Note that this representation provides a simplified illustration of some possible reactions rather than an exhaustive account of all interactions

that collides with the nuclei of a nitrogen atom in the air. These collisions lead to the production of secondary particles, including protons, neutrons, pions  $\pi$ , kaons *K*, and muons  $\mu$ . This process continues until the secondary particles have insufficient energy to sustain further interactions. Pions and kaons are unstable particles with short lifespans. They rapidly decay into various particles, including muons, electrons  $e^-$ , positron  $e^+$  (antiparticle of electrons), neutrinos  $\nu$ , and photons  $\gamma$ .

Cosmic ray air showers are comprised of various secondary particles, each with unique properties. Muons are particularly noteworthy due to their relatively long lifespan compared to pions and kaons, despite still being short-lived compared to stable particles like protons and electrons. Although their average lifetime is just 2.2 microseconds; this allows them to travel several kilometers through the atmosphere before decaying. Similar to electrons, muons are fundamental particles. However, their much greater mass grants them significantly higher penetration power. Muons can traverse several centimeters of materials like silicon, potentially reaching sensitive electronic components within spacecraft or even electronics on the ground. Historically, secondary neutrons were considered the primary contributors of radiation damage in electronic devices exposed to the atmospheric environment. However, with advancements in miniaturization and increased device sensitivity, muons pose a growing threat to system reliability by inducing radiation damage in microelectronics [14–17].

It is important to note that the cascade of secondary interactions triggered by a high-energy cosmic ray is a complex process with numerous possible reaction pathways. These pathways depend heavily on the specific energy, angle of incidence, and characteristics of the primary particle, along with the properties of the target atoms it interacts with. While Fig. 1.5 provides a simplified illustration, the true nature of these interactions involves a vast array of potential reactions. The flux and composition of atmospheric radiation are subject to fluctuation, influenced by various factors. Solar activity notably impacts the influx of particles bombarding the upper atmosphere, while the Earth's nonuniform magnetic field results in spatial variations in radiation intensity and composition. Regions with weaker magnetic fields, such as the South Atlantic Anomaly discussed earlier, experience heightened fluxes of energetic particles.

Altitude also plays a pivotal role. As we descend through the atmosphere, particle flux initially rises due to collisions with atmospheric nuclei, generating secondary particles. This increase peaks at the *Pfotzer maximum*, after which flux diminishes due to energy loss through interactions, absorption by atmospheric molecules, and decay of unstable particles [18]. For instance, neutron flux increases with decreasing altitude, reaching its peak density of approximately  $10^4$  neutrons per square centimeter per hour (n/cm<sup>2</sup>/h) at around 20 km [19, 20]. However, this density drastically declines to about 20 n/cm<sup>2</sup>/h at ground level, a mere fraction of its peak value, approximately 0.2%. Apart from neutrons and muons, protons are also a concern for ground-level atmospheric applications, although typically exhibiting lower fluxes when compared to energies up to 400 MeV [21].

While the probability of failure induced by secondary cosmic ray particles is relatively low at ground level, it can still be a concern for safety-critical systems that rely heavily on electronics. These systems require extremely high reliability, and even a small chance of failure can have significant consequences. Therefore, understanding the particle flux and composition at different altitudes and locations is crucial for assessing the radiation threat and designing reliable systems for atmospheric applications.

#### 1.2.3 Accelerator Environment

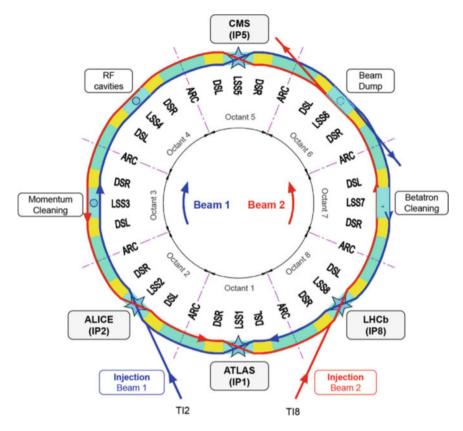

Another hostile environment with a very particular radiation field is encountered in particle accelerators used in high-energy physics research laboratories. A very good example is the world's largest collider, the large hadron collider (LHC) in the European Organization for Nuclear Research (CERN) in which, in its current

Fig. 1.6 Schematic of the LHC layout division into octants where the main experiments are hosted in IP1 (ATLAS), IP2 (ALICE), IP5 (CMS) and IP8 (LHCb) (Adapted from [22])

design, protons can be accelerated up to 7 TeV. The LHC is a circular collider as shown in the layout in Fig. 1.6 where the eight octants, the interaction points (IP), and the direction of the beams are illustrated. There are four main interaction points where the physics experiments are hosted: interaction point 1 (IP1) hosts the *ATLAS experiment*, the general-purpose LHC experiment where the world's largest particle detector is installed; interaction point 2 (IP2) hosts the *ALICE experiment*, a large ion collider detector dedicated to heavy-ion physics; interaction point 5 (IP5) hosts the compact muon solenoid (*CMS*) *experiment*, which is another general-purpose detector similar to ATLAS with a broad physics program and a different magnet system; and, lastly, the interaction point 8 (IP8) hosts the *LHCb experiment*, in which, different from the previous experiments, the large hadron collider beauty is a collection of subdetectors used to detect the forward particles from the collisions and to investigate the beauty quark (b quark).

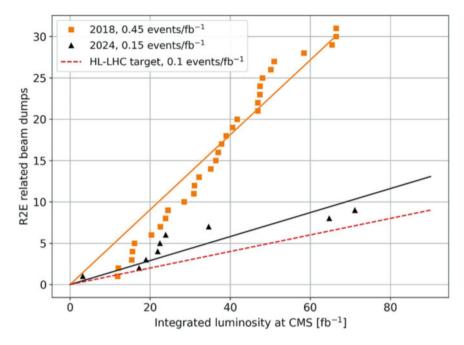

The performance of particle colliders such as the LHC is mostly associated with its physics production, i.e., the number of particle collisions and the production of new physics. Generally, it is measured by the energy that the injected particles can be accelerated to and by the *integrated luminosity* (number of observed inelastic collisions) measured by their detectors. During the LHC physics run 2 (2015–2018), an average integrated luminosity of 50 fb<sup>-1</sup> (femtobarns) per year was achieved. This high luminosity allowed for a significant number of collision events to be recorded and analyzed. However, with the high luminosity (HL) LHC upgrade project, the nominal annual integrated luminosity and the corresponding increase in the number of collisions also lead to higher radiation levels in different areas of the accelerator. These elevated radiation levels can pose operational challenges, such as reduced beam availability caused by beam dumps resulting from magnet quenching (loss of superconductivity) or system failures due to radiation effects on electronics.

**Luminosity** is a measurement of how many collisions a particle collider can produce. It is usually expressed as an integral over the physics run duration and the unit is the *inverse femtobarn*  $(fb^{-1})$  corresponding to roughly  $10^{14}$  particle interactions at TeV energies [23].

The LHC radiation environment consists of a mixed field with a variety of particles and energies which vary along the different locations in the accelerator complex. It depends not only on the different beam loss mechanisms at play but also on the accelerator settings such as the beam intensity and collimator settings [23, 24]. In this context, there are three main sources of radiation generally related to beam losses:

- 1. Beam Interaction with Residual Gas: the particles are accelerated in a vacuum pipe to prevent their interaction with air molecules and therefore the beam intensity loss. However, despite the very high vacuum levels, there is still some remaining (residual) gas in the vacuum chamber. When the protons interact with these residual molecules, a radiation cascade of secondary particles similar to the one observed in the atmospheric environment is also observed in the accelerator tunnels. This beam loss mechanism is the main contributor to the radiation level in the arc sections in the LHC ring, and it is expected to scale linearly with the *integrated intensity* (number of injected particles) and the residual gas density in the vacuum chamber [25].

- 2. Beam Interaction with Machine Elements: despite the strong magnetic field applied to control and guide the bunch of particles within the beam pipes, some particles, known as *halo particles*, can deviate from the desired trajectory and interact with different beam line elements leading to their activation and increased radiation levels. For instance, to prevent the damage of sensitive components and possible magnet quenches and to provide a protection against uncontrolled beam losses, collimators are used to clean up the beam by absorbing the halo particles. However, the collimator locations are hotspots for radiation levels as a large number of secondary particles is produced from these halo collisions.

3. Debris from Collisions in the physics experiments: another common source of radiation is the collision debris from the proton-proton inelastic interactions in the four main LHC experiments shown in Fig. 1.6. For every single proton-proton collision, an average multiplicity of 120 secondary particles are generated and intercepted by the detectors placed in the experiments [23]. However, some of these secondaries are able to reach out of the detector zone and collide with the beam elements in the surrounding area, increasing the radiation levels. Different from the beam losses due to the beam-gas interactions, the radiation levels induced by collision debris are luminosity driven and therefore scale with the integrated luminosity of each experiment [25].

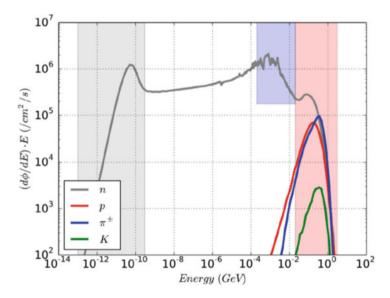

The monitoring of radiation levels in particle accelerators serves multiple crucial purposes. It not only safeguards the integrity and performance of the accelerator itself but also ensures the safety of personnel working in the underground beam lines. While delving into the intricacies of radiation protection measures falls beyond the scope of this book, it is essential to acknowledge their significance in such radioactive environments. Additionally, radiation hardness assurance (RHA) methodologies play a pivotal role in qualifying components and systems to withstand the harsh radiation environment, mitigating the risk of system failures induced by high radiation levels [23, 26–28]. When examining the impact of radiation on electronics, particular attention is given to high-energy hadrons (HEH) and neutrons, as they dominate the particle spectrum within the LHC environment. Figure 1.7 presents a representative lethargy spectrum encountered at the LHC, considering the relevant hadrons such as protons, charged pions, and kaons, as well as neutrons. This

**Fig. 1.7** FLUKA-simulated lethargy spectra for an LHC-like test location at the CHARM test facility at CERN. The different shaded regions approximately represent the thermal neutron (gray), intermediate neutron (blue), and HEH fluxes (red) [32]

| Table 1.1Approximatehigh-energy hadron (HEH)annual fluxes from space to | Spectrum<br>Ground level       | $\Phi \text{ HEH } (/\text{cm}^2/\text{yr})$ $\sim 2 \cdot 10^5$ |

|-------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------|

| accelerator radiation                                                   | Avionics                       | $\sim 2 \cdot 10^7$                                              |

| environments                                                            | ISS orbit                      | $\sim 7 \cdot 10^8$                                              |

|                                                                         | LEO orbit (800 km)             | $\sim 3 \cdot 10^9$                                              |

|                                                                         | LHC ring + transfer lines      | $\sim 10^6 - 10^{12}$                                            |

|                                                                         | Super proton synchrotron (SPS) | $\sim 10^{6} - 10^{12}$                                          |

|                                                                         | Proton synchrotron (PS)        | $\sim 10^{10} - 10^{11}$                                         |

|                                                                         | PS booster                     | $\sim 10^9 - 10^{11}$                                            |

spectrum was simulated using FLUKA, a widely validated Monte Carlo transport code extensively utilized in accelerator research and beyond [29–31]. As depicted in Fig. 1.7, three distinct energy ranges stand out, with varying abundances and effects on electronic reliability. High-energy hadrons exhibit a prominent flux peak in the several hundred MeV range, while neutrons span a range from thermal energies up to 20 MeV [32]. These energy ranges are of significant relevance when assessing the potential impact of radiation on electronic systems. By comprehending the characteristics and intensities of these particles, strategies can be devised to harden electronics against radiation-induced challenges and ensure their reliable operation in the demanding environment of particle accelerators [27].

**Hadrons** are subatomic particles composed of two or more quarks held together by the strong nuclear force, such as protons, neutrons, pions, and kaons. The term high-energy hadrons (HEH) is widely used in the accelerator environment to design the hadrons with energies in the MeV, which are quite relevant in regard to inducing radiation events on electronic components.

In Table 1.1, the approximate HEH annual fluxes are presented for the different radiation environments, from space, i.e., the International Space Station (ISS) and low-Earth orbits, to ground and accelerator environments. For instance, the HEH fluxes at CERN's accelerator complex, from the injector chain to the LHC ring, can be comparable to the fluxes observed in commercial flights (around  $10^7/\text{cm}^2/\text{yr}$ ) and in space ( $10^8 - 10^9/\text{cm}^2/\text{yr}$ ); however, depending on the location in machine, it can reach levels way beyond (up to  $10^{12}/\text{cm}^2/\text{yr}$ ).

#### **1.3** Particle Interaction Mechanisms

This section serves as an introduction to particle-matter interactions, focused mainly on important mechanisms capable of inducing radiation effects on electronic components. These effects can be broadly classified into two groups: cumulative effects, which encompass total ionizing dose (TID) and displacement damage (DD) and single-event effects (SEEs), a category of effects where a single particle impact can disrupt the proper operation of electronic devices. Regardless of the specific effect on the electronic device, it always originates from one or more particles that deposit energy in the device. In this book, our focus is primarily on the study and mitigation of single-event effects, more specifically on the nondestructive effects known as *soft errors*. Therefore, the subsequent sections will be dedicated to comprehending these effects in greater detail.

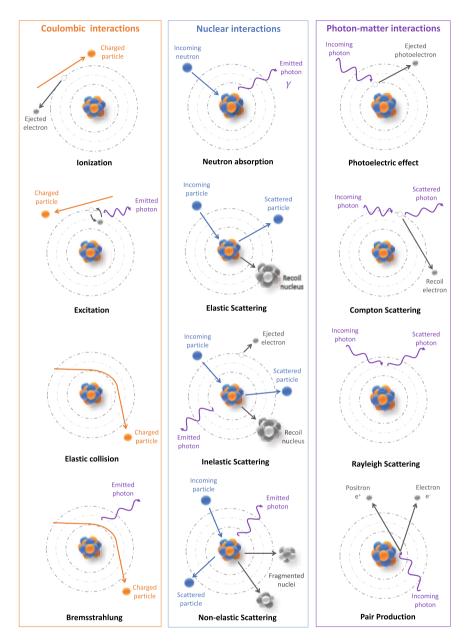

Numerous types of particles have the capability to deposit energy in a device and induce SEEs. Radiation-matter interactions are strongly dependent on the characteristics of the particle, including its charge, mass, and energy. For instance, charged particles like protons engage in both nuclear reactions and Coulombic interactions with the orbital electrons of the target nucleus. Conversely, neutrons, being uncharged, can traverse the electronic clouds of an atom without interaction, making them highly penetrating particles that solely interact and lose energy with atomic nuclei. Figure 1.8 outlines the main Coulombic and nuclear interactions, as well as photon-matter interactions, which are essential for understanding the impact of radiation on electronics.

- **Coulombic Interactions:** *Ionization*, when a charged particle (e.g., proton) interacts with the electric field of an orbital electron, it can remove it from its orbit, creating an electron-hole pair, where the vacancy left behind by the ejected electron acts like a positive charge carrier (hole); *Excitation*, occurs when the interaction with the electric field only elevates the electron to a higher energy level within the same atom and upon returning to its ground state, the electron releases energy in the form of a photon; *Elastic collision*, when a charged particle is deflected by the atomic nucleus and the total kinetic energy is conserved; *Bremsstrahlung*, occurs when a charged particle accelerates or decelerates, emitting electromagnetic radiation (photons) due to this change in motion.

- Nuclear Reactions: Neutron absorption or capture, occurs when a low-energy neutron collides with a nucleus, leading to the emission of gamma rays as the excess energy is released; in *elastic scattering*, the incident particle collides with the nucleus, transferring some kinetic energy to the nucleus. The nucleus recoils, while the incident particle is scattered in a different direction; however, the total kinetic energy of the system remains conserved; on the other hand, in *inelastic scattering*, the total kinetic energy is not conserved and the collision can induce the emission of photons or ejection of electrons; a similar phenomenon is observed in *non-elastic scattering*, where the nucleus is fragmented into secondary particles, neutrons, or other ions species.

- **Photon-matter interactions:** *Photoelectric effect*, a photon transfers all its energy to a tightly bound orbital electron, ejecting it from the atom with a kinetic energy equal to the difference between the energy of the incident photon and the binding energy; *compton scattering* occurs when a photon interacts with a relatively free electron (compared to tightly bound inner-shell electrons), imparting a portion of its energy to the electron, which recoils with some kinetic

Fig. 1.8 Simplified representation of main particle-matter mechanisms (Coulombic, nuclear, and photon-matter interactions)

energy. The remaining energy of the photon is carried away by a scattered photon with a longer wavelength (lower energy) compared to the incident photon; *Rayleigh scattering*, also known as coherent scattering, occurs when a low-energy photon interacts with an atom and is scattered elastically. The scattered photon retains its energy but deflects in a different direction; lastly, *pair production*, high-energy photons (typically exceeding 1.022 MeV) can interact with the strong electric field near a nucleus, leading to the creation of an electron-positron pair. The positron is the antiparticle of the electron and has the same mass but a positive charge. The minimum energy requirement of at least 1.022 MeV for a photon arises from the fact that the resting mass of both the electron and positron, when expressed in energy units, is 0.511 MeV each. Consequently, for the creation of an electron-positron pair, a minimum total energy of 1.022 MeV is necessary, corresponding to twice the energy of a single electron or positron.

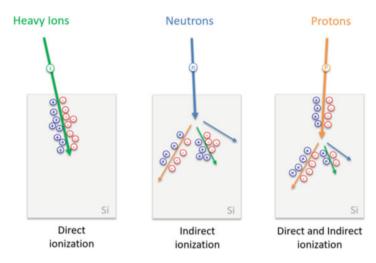

#### 1.4 Energy Deposition

Originally, single-event effects (SEEs) were primarily associated with neutrons, protons, or heavier ions. It is worth noting, however, that certain studies have shown that SEEs can also be triggered by electrons [33–36] or muons [14–17]. Nevertheless, for the purposes of our discussion, these particles will not be considered. SEEs primarily result from ionization, occurring directly with ions and protons, and indirectly in the case of neutrons due to nuclear reactions. While ions and protons can directly ionize the target material, they can also engage in nuclear reactions with the atomic nucleus. For heavy ions, the contribution from nuclear reactions is typically insignificant compared to direct ionization. However, for protons, both direct and indirect ionization processes are significant. Figure 1.9 illustrates the direct and indirect ionization processes for a heavy ion and a neutron, respectively.

Historically, the direct ionization of protons was not a major concern as they had limited capability to ionize matter directly. Consequently, only high-energy protons (E > 20 MeV) were considered a threat to electronic systems due to their capacity to induce nuclear reactions in silicon and produce secondary ions with higher ionization potential. However, in deeply scaled technologies, low-energy protons (E < 3 MeV) have been identified as significant contributors to soft error rates in space applications and beyond [37–39].

The loss of energy is generally quantified by the concept of *stopping power*, *S*, also called *specific energy loss*, which is defined as the differential energy loss dE dividing by the differential path length dx:

$$S = -\frac{dE}{dx}$$

(1.1)

Fig. 1.9 Representation of direct ionization and indirect ionization for heavy ions, neutrons, and protons interaction with matter (Si stands for silicon)

where the minus sign is a common way to deal with a positive quantity (the energy loss dE is a negative variation of energy). The stopping power unit is given in megaelectronvolts per centimeter (MeV/cm). In the radiation effect community, the stopping power is generally divided by the mass density of the material, making the new quantity independent of its phase. This new quantity, called *mass stopping power*,  $S_m$  is then:

$$S_{\rm m} = -\frac{1}{\rho} \frac{dE}{dx} \tag{1.2}$$

where  $\rho$  is the density of the target material. For electronics, the silicon density is used,  $\rho_{Si} = 2.32 \text{ g} \cdot \text{cm}^{-3}$ . The mass stopping power unit is given in megaelectronvolts square centimeter per milligram (MeV  $\cdot \text{cm}^2/\text{mg}$ ).

Another important quantity for charged particle is the *linear energy transfer*, or **LET**. While the stopping power measures the energy loss of the particle, the LET measures the energy absorbed in matter. The difference comes from the energy loss by radiation, which is actually not significant for ions. Through misuse of language, the word *LET* is often use instead of *stopping power* or even instead of *mass stopping power*.

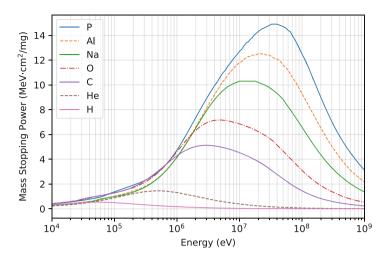

The stopping power depends not only on the particle type but also on its energy and the target material where ionization takes place. The variation of mass stopping power as a function of the ion energy in silicon was calculated for different ions using the stopping and range of ions in matter (SRIM) code [40] as shown in Fig. 1.10.

**Fig. 1.10** Variation of the stopping power as a function of energy for different ions in silicon (Data obtained from SRIM [40])

The stopping power of a particle increases with energy until it reaches the *Bragg peak*, which represents the maximum value of stopping power. It is important to note that the Bragg peak for hydrogen (protons) is significantly lower compared to heavier ions like phosphorus. In general, the stopping power at the Bragg peak is higher for ions with a higher atomic number (Z). This is because the energy loss is primarily governed by the Coulomb effect, and at higher Z, the interaction between the particle and the medium is stronger. For energies above the Bragg peak, the stopping power decreases as the particle energy increases. It is interesting to observe that different ion species with different energies can yield the same stopping power value. This is because energy loss involves interactions with both electrons and nuclei of the medium. Therefore, the stopping power is typically considered as the sum of two contributions:

$$S_{\rm m} = -\frac{1}{\rho} \frac{dE}{dx} \Big|_{elec} - \frac{1}{\rho} \frac{dE}{dx} \Big|_{nuc}$$

(1.3)

The first term represents the interaction of the particle with electrons. When sufficient energy is transferred, it leads to the generation of electron-hole pairs. This process is known as *ionization*, as an electron moves from the valence band to the conduction band. The second term accounts for the interaction of the particle with the nuclei of the medium. This interaction can be mediated by either the Coulomb force or the strong nuclear force. In the case of Coulomb interactions, the target nucleus can undergo vibration or recoil, leading to *displacement damage*. Alternatively, if the interaction is governed by the strong force, a *nuclear reaction* can occur, causing the nucleus to break up into fragments.

While neutrons, protons, and heavy ions interact with matter in distinct ways, they all ultimately result in the ionization of the material, either directly or indirectly. This ionization process can potentially trigger SEEs in electronic devices. Therefore, understanding the stopping power of these ions, both primary and secondary, is of prime importance for the assessment of their impact and the mitigation of the associated risks.

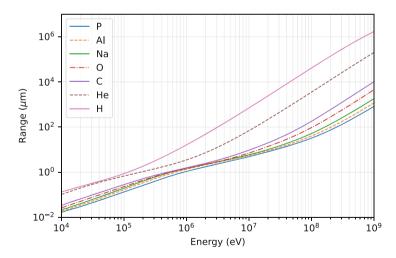

Another crucial quantity of interest for charged particles is the *range*, denoted as *R*. It is defined as the distance the particle can travel before being at rest. The range is related to the stopping power through the following relationship:

$$\mathbf{R} = \int_{E_{init}}^{0} \frac{1}{-\frac{\mathrm{dE}}{\mathrm{dx}}} \,\mathrm{dx} \tag{1.4}$$

where  $E_{init}$  is the initial energy of the particle. Particles with high stopping power experience significant energy loss, resulting in a short range of travel. This can be observed in Fig. 1.11, which presents examples of particle ranges calculated using SRIM. The figure illustrates how the range varies for different particles, highlighting the impact of their stopping power on the distance they can travel in a material.

The energy deposition in the semiconductor leads to a nearly linear path of *electron-hole pairs* (ehp). The minimum energy required to generate an electron-

**Fig. 1.11** Variation of the range as a function of energy for different ions in silicon (Data obtained from SRIM [40])

#### 1.4 Energy Deposition

|                   |        | Bandgap energy | Ionization energy |

|-------------------|--------|----------------|-------------------|

| Material          | Symbol | $E_g$ (eV)     | $E_{ehp}(eV)$     |

| Germanium         | Ge     | 0.66           | 2.4               |

| Silicon           | Si     | 1.11           | 3.6               |

| Indium phosphide  | InP    | 1.34           | 4.2               |

| Gallium arsenide  | GaAs   | 1.43           | 4.5               |

| Gallium phosphide | GaP    | 2.26           | 6.7               |

| Silicon carbide   | 3C-SiC | 2.35           | 7.0               |

|                   | 6H-SiC | 3.08           | 9.0               |

|                   | 4H-SiC | 3.28           | 9.5               |

| Gallium nitride   | GaN    | 3.4            | 9.8               |

| Aluminum nitride  | AlN    | 6.24           | 17.6              |

**Table 1.2** Bandgap energy  $E_g$  and ionization energy  $E_{ehp}$  for different semiconductor materials

hole pair can be estimated based on the *bandgap energy*  $E_g$  of the material using Eq. 1.5 [41]:

$$E_{ehp} = 2.73E_g + 0.55 \tag{1.5}$$

For silicon-based devices, the silicon bandgap energy  $E_g$  is equal to 1.11 eV; therefore, based on Eq. 1.5, the average *ionization energy*  $E_{ehp}$  in silicon is approximately 3.6 eV/ehp. In Table 1.2, for different semiconductor materials, the bandgap energy  $E_g$  and the corresponding ionization energy  $E_{ehp}$  calculated using Eq. 1.5 are presented. The higher the bandgap energy of the material, the higher is the energy required to ionize the matter and create electron-hole pairs. This explains why wide-bandgap electronics such as the SiC- and GaN-based devices show a better radiation performance overall.

Based on the assumption that the stopping power is constant as a consequence of the small ionization path length l within the sensitive volume of a device, the deposited energy can be converted in *deposited charge*  $Q_D$  by following Eq. 1.6:

$$Q_{\rm D} = \frac{q \cdot S \cdot \rho \cdot l}{E_{ehp}} \tag{1.6}$$

where q is the elementary charge and S is the so-called *surface mass stopping* power which refers to the mass stopping power value when the particle enters the sensitive volume, i.e., after traveling and losing energy through all the back-end-of-line (BEOL) layers. The deposited charge  $Q_D$  needs to be collected by a sensitive node of a circuit and exceeds the minimum charge necessary to induce a SEE, known as *critical charge Qcrit*. The charge collection mechanisms are briefly described in the following section.

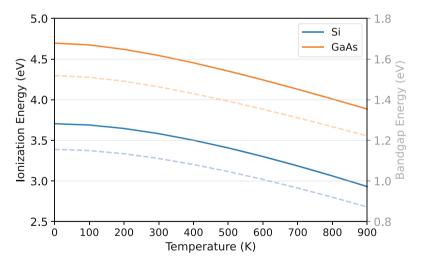

Another quite relevant aspect, when studying radiation effects on electronics, is the temperature dependence of many mechanisms at the device and circuit levels. For instance, the bandgap energy of a semiconductor material is temperature dependent and can be described using Varshni's Equation [42]:

$$\mathbf{E}_{g}[\mathbf{T}] = E_{g}[\mathbf{0}] - \frac{\alpha \cdot T^{2}}{T + \beta}$$

(1.7)

where  $E_g[0]$  is the bandgap energy for temperature *T* equals to 0 K, while  $\alpha$  and  $\beta$  are fitting parameter to experimental data. These three parameters are presented in Table 1.3 for the three main semiconductor materials. In Fig. 1.12, the bandgap and ionization energy for silicon and gallium arsenide (GaAs) are shown for a wide range of temperature measure in *K* and calculated with Eq. 1.7. As mentioned previously, lower ionization energy is observed in Si due to its lower bandgap energy when compared to GaAs. However, as the temperature is increased, both materials show a reduction in the ionization energy. Although the decrease is minimal, it can increase the number of electron-hole pairs that a particle can generate and increase the total deposited charge. Other mechanisms are also affected by temperature, as it will be shown in the following chapters, such as carrier mobility and resistance.

| <b>Table 1.3</b> Fitting parametersfor Varshni's equation to | Material         | Symbol | $E_g[0]$ | α       | β    |

|--------------------------------------------------------------|------------------|--------|----------|---------|------|

| consider the temperature                                     | Germanium        | Ge     | 0.7412   | 4.561   | 210  |

| dependence of bandgap                                        | Silicon          | Si     | 1.557    | 7.021   | 1108 |

| energy of Ge, Si, GaAs, and                                  | Gallium arsenide | GaAs   | 1.5216   | 8.871   | 572  |

| 6H-SiC                                                       | Silicon carbide  | 6H-SiC | 3.024    | -0.3055 | -311 |

Fig. 1.12 Ionization energy (solid lines) and bandgap energy (dashed lines) for silicon and gallium arsenide as a function of temperature

Besides depending on the material, the *ionization energy*  $E_{ehp}$  is also **temperature dependent**. As the temperature increases, the bandgap energy reduces and, therefore, the ionization energy is also reduced.

#### **1.5 Charge Collection**

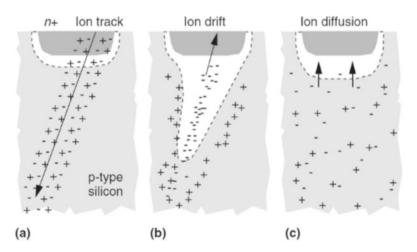

After the energy deposition in the semiconductor material, the generated carriers are transported and collected by the junctions of the device. In the context of SEE, there are two main transport mechanisms that play a crucial role: the *drift* and the *diffusion*. Figure 1.13 illustrates the ionization process of an ion in a reverse-biased p-n junction and the subsequent carrier transport mechanisms.

Drift is a transport mechanism that is primarily governed by the electric field existing within the p-n junctions of sensitive electronic devices. When a particle directly impacts the sensitive collecting area of the circuit, the resulting carriers experience rapid collection due to the influence of the high electric field present in the reverse-biased p-n junction. In semiconductor materials, the drift current  $J_{drift}$  can be described as a function of the applied electrical field  $\mathscr{E}$  and the conductance G, as expressed by the equation:

$$J_{drift} = G \cdot \mathscr{E} \tag{1.8}$$

Fig. 1.13 Charge collection mechanisms due to an ion strike in a p-n junction (Adapted from [43])

Finally, by knowing that the conductance G is proportional to the the carrier mobility  $\mu$  and to the carrier concentrations n and p, the total drift current  $J_{drift}$  can be described as [44]:

$$J_{drift} = q(\mu_n n + \mu_p p) \cdot \mathscr{E}$$

(1.9)

where q is the elemental charge  $(q = 1.6 \times 10^{-19} C)$ .

On the other hand, diffusion is a carrier transport mechanism governed by the carrier concentration gradients. Therefore, whenever there is a gradient of carriers, they are transported from regions with high to low concentrations to reach a state of uniformity [44]. The diffusion current J can be obtained based on Fick's Law:

$$J_{Dn} = q D_n \frac{dn}{dx} \tag{1.10}$$

$$J_{Dp} = -q D_p \frac{\mathrm{d}p}{\mathrm{d}x} \tag{1.11}$$

where  $D_n$  and  $D_p$  are the diffusion coefficients and dn/dx and dp/dx are gradient of carrier concentrations for electrons and holes, respectively. As the diffusion is governed by random thermal motion of carriers and scattering, it has a direct relationship with the mobility of carriers  $\mu$  and, therefore, the diffusion coefficients can be described as [44]:

$$D_{n,p} = \left(\frac{kT}{q}\right) \mu_{n,p} \tag{1.12}$$

where, at room temperature (300 K), (kT/q) is equal to 0.0259 V.

Considering the one-dimensional case, the total current J can be calculated using Eq. 1.9 for the drift component, and for the diffusion component using Eqs. 1.10 and 1.14 as shown below:

$$J_n = q \cdot \left(\mu_n n \mathscr{E} + D_n \frac{\mathrm{dn}}{\mathrm{dx}}\right) \tag{1.13}$$

$$J_p = q \cdot \left(\mu_p p \mathscr{E} - D_p \frac{\mathrm{d}p}{\mathrm{d}x}\right) \tag{1.14}$$

If we want to determine the evolution of carriers concentrations during time, we need to solve the transport equations that are given by:

$$q\frac{\partial n}{\partial t} = \nabla J_n - q \times R \tag{1.15}$$

$$q\frac{\partial p}{\partial t} = -\nabla J_p + q \times R \tag{1.16}$$

where R is the recombination rate of electron-hole pairs.

Solving transport equations is a long and complex process that requires to perform approximations and use numerical tools, called technology computer-aided design (TCAD) tools.

Another very interesting effect occurs when the particle strikes in or near the p-n junction, as shown in Fig. 1.13b. The depletion region, also known as the space charge region, is increased, and therefore, the drift collection efficiency is also increased. This phenomenon is known as *funneling effect* and together with drift, they are two very fast processes due to the presence of the high electric field in the junction. Following these processes, the remaining carriers are collected by diffusion process or they go through recombination.

Understanding these intricate processes is crucial for comprehending the behavior of semiconductor devices, particularly in relation to their response to particle interactions. By examining the interplay between drift, funneling effect, diffusion, and recombination, we can gain valuable insights into the overall performance and reliability of these devices.

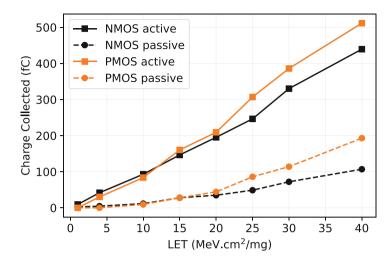

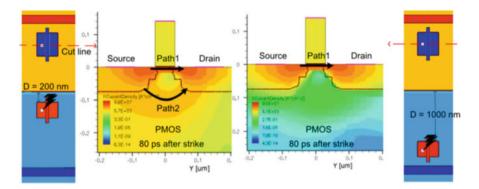

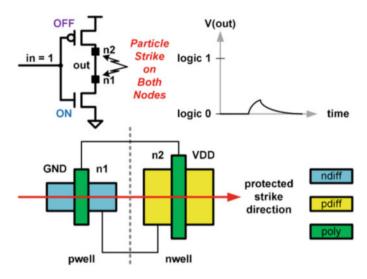

#### 1.5.1 Charge Sharing and Pulse Quenching Effect

As technology advances and transistors are placed in closer proximity to each other, the critical charge required to trigger an SEE is reduced. Consequently, a single incident particle is able to induce sufficient charge collection from multiple neighboring electrodes. This phenomenon is known as charge sharing effect. The work developed by Amusan et al. [45] provides an analysis of the charge sharing effect in adjacent N-channel metal-oxide semiconductor (NMOS) and P-channel metal-oxide semiconductor (PMOS) transistors based on TCAD simulations. The 130 nm CMOS devices, based on the International Business Machines corporation (IBM) twin well technology, were characterized using advanced simulation tools such as Synopsis DEVISE and DESSIS. In the simulation setup, a particle hit was precisely targeted at the center of the drain region, perpendicular to the surface of the device structure. It is worth noting that for the purpose of these simulations, the influence of angular effects was omitted in the analysis. The authors used two particular notations: active device, which refers to the device directly struck by the particle and actively collecting the carriers, and the **passive device**, which represents the device not directly impacted by the particle but passively collecting the diffused carriers. In Fig. 1.14, the collected charge is shown for the active and passive devices when PMOS and NMOS transistors are used.

The results of this study clearly demonstrate that passive PMOS devices are capable of collecting a greater amount of charge compared to passive NMOS devices. Specifically, the passive PMOS device collected approximately 40% of the charge collected by the active PMOS device, while the passive NMOS transistor

Fig. 1.14 Charge collected by PMOS and NMOS for normal particle hits at the center of the drain region of the active device (Data from [45])

collected less than 25% of the charge. The authors attribute this discrepancy to the disparity in carrier diffusion coefficients between electrons and holes, as well as the bipolar amplification effect that enhances charge collection in PMOS devices [45, 46].

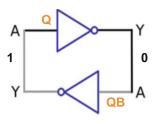

While the charge sharing mechanism is responsible for the increased SEE sensitivity in deeply scaled technologies, it has also been shown to reduce the pulse width of SETs in combinational cells [47, 48]. Due to the similar time constant for the circuit delay and the diffusion process, the radiation-induced transient is able to activate the charge collection in electrodes from following stage of circuits in such a way that the resultant transient is shortened (i.e., quenched). This phenomenon is referred to as the pulse quenching effect (PQE). To observe the PQE in a circuit, an inverting relationship between logic stages is required. Both charge sharing and the pulse quenching effect are intricate and critical mechanisms that heavily depend on the specific device technology and design strategies employed. Therefore, acquiring a comprehensive understanding of their impact is of utmost importance for accurately assessing the sensitivity of modern electronic components to single-event effects.

#### 1.6 Summary

In this chapter, we explored the fundamental concepts surrounding the study of radiation effects in electronics. Our exploration begins by unraveling the complex dynamics and composition of the space and atmospheric radiation environment. At the heart of this cosmic interplay is the Sun, which acts as the primary modulator of

solar particle radiation and galactic cosmic rays. For missions focused on Earth's vicinity, it becomes crucial to consider the impact of the Van Allen radiation belts on on-board electronic systems. Furthermore, in low-orbit and atmospheric applications like satellites and aviation, the South Atlantic Anomaly region exhibits a heightened proton flux, necessitating careful attention.

Depending on the type of incident radiation, direct and indirect ionization processes can occur within electronic components, resulting in energy deposition and charge collection by critical device electrodes. In advanced technology nodes, a single particle strike has the potential to impact multiple devices within a chip, resulting in the diffusion of charges across multiple critical nodes—a phenomenon known as the charge sharing effect. Looking ahead, the subsequent chapter will delve into the radiation-induced effects at the circuit level, specifically focusing on the well-known single-event effects (SEEs).

#### Highlights

- Three main natural sources of radiation should be considered in space and atmospheric applications: the *solar energetic particles* (SEPs), *galactic cosmic rays* (GCRs), and geomagnetically trapped particle radiation (*Van Allen's radiation belts*).

- The Sun's activity is the main radiation modulator of the radiation environment near Earth, but also impacts ground-level applications, such as the Carrington event.

- A misalignment between the Earth's geomagnetic and rotational axes generates a weakness in the geomagnetic field over South America, leading to higher particle fluxes in this region known as the South Atlantic Anomaly (SAA).

- With the technology scaling, neutrons but also muons are considered a threat to the electronic system reliability.

- In an accelerator environment, there are also three main sources of radiation: beam interaction with residual gas, beam interaction with machine elements, and debris from collisions in physics experiments.

- The high-energy hadrons (HEH) and neutrons are the most abundant and relevant particles in the LHC environment in terms of inducing electronic failures.

- An energetic particle can deposit energy either through direct ionization (ions, protons, etc.) or by indirect ionization (protons and neutrons).

- Two main mechanisms are responsible for charge collection in a device: drift due to the electric field present in the p-n junctions and diffusion due to the carrier concentration gradients.

- With the miniaturization of transistor technology, a single particle is able to deposit energy in multiple devices, and therefore charge sharing effect is prominent in highly scaled technologies.

#### References

- 1. NASA website. https://www.nasa.gov/

- ECSS-E ESA. St-10-04c rev. 1 space engineering. Space environment. ESA-ESTEC, Noordwijk, Jun, 2020.

- MA Shea and DF Smart. A comparison of energetic solar proton events during the declining phase of four solar cycles (cycles 19–22). Advances in Space Research, 16 (9): 37–46, 1995.

- 4. Space weather prediction center. https://www.swpc.noaa.gov/

- 5. Scott E Forbush. World-wide cosmic ray variations, 1937–1952. Journal of Geophysical Research, 59 (4): 525–542, 1954.

- 6. IV Dorman and LI Dorman. Solar wind properties obtained from the study of the 11-year cosmic-ray cycle: 1. *Journal of Geophysical Research*, 72 (5): 1513–1520, 1967.

- K Nagashima and I Morishita. Twenty-two year modulation of cosmic rays associated with polarity reversal of polar magnetic field of the sun. *Planetary and Space Science*, 28 (2): 195– 205, 1980.

- Richard C Carrington. Description of a singular appearance seen in the sun on September 1, 1859. *Monthly Notices of the Royal Astronomical Society*, 20: 13–15, 1859.

- 9. Edward W Cliver and William F Dietrich. The 1859 space weather event revisited: limits of extreme activity. *Journal of Space Weather and Space Climate*, 3: A31, 2013.

- 10. Stuart Clark. Solar surprise. New Scientist, 254 (3387): 38-41, 2022.

- 11. Ryuho Kataoka, Daikou Shiota, Hitoshi Fujiwara, Hidekatsu Jin, Chihiro Tao, Hiroyuki Shinagawa, and Yasunobu Miyoshi. Unexpected space weather causing the reentry of 38 starlink satellites in february 2022. doi: https://doi.org/10.31223/X5GH0X.

- Marco Durante and Francis A Cucinotta. Physical basis of radiation protection in space travel. *Reviews of Modern Physics*, 83 (4): 1245, 2011.

- 13. The omere 5.3 software by trad and cnes. URL http://www.trad.fr/en/space/omere-software

- 14. Brian D Sierawski, Marcus H Mendenhall, Robert A Reed, Michael A Clemens, Robert A Weller, Ronald D Schrimpf, Ewart W Blackmore, Michael Trinczek, Bassam Hitti, Jonathan A Pellish, et al. Muon-induced single event upsets in deep-submicron technology. *IEEE Transactions on Nuclear Science*, 57 (6): 3273–3278, 2010.

- G Hubert, L Artola, and D Regis. Impact of scaling on the soft error sensitivity of bulk, FDSOI and FinFET technologies due to atmospheric radiation. *Integration, the VLSI journal*, 50: 39– 47, 2015.

- 16. Angelo Infantino, Ewart W Blackmore, Markus Brugger, Rubén García Alía, Matthew Stukel, and Michael Trinczek. Fluka Monte Carlo assessment of the terrestrial muon flux at low energies and comparison against experimental measurements. *Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment*, 838: 109–116, 2016.

- Takashi Kato, Motonobu Tampo, Soshi Takeshita, Hiroki Tanaka, Hideya Matsuyama, Masanori Hashimoto, and Yasuhiro Miyake. Muon-induced single-event upsets in 20-nm SRAMs: Comparative characterization with neutrons and alpha particles. *IEEE Transactions* on Nuclear Science, 68 (7): 1436–1444, 2021.

- 18. Peter KF Grieder. Cosmic rays at Earth. Elsevier, 2001.

- 19. Janet L Barth, CS Dyer, and EG Stassinopoulos. Space, atmospheric, and terrestrial radiation environments. *IEEE Transactions on nuclear science*, 50 (3): 466–482, 2003.

- 20. MS Gordon, P Goldhagen, KP Rodbell, TH Zabel, HHK Tang, JM Clem, and Paul Bailey. Measurement of the flux and energy spectrum of cosmic-ray induced neutrons on the ground. *IEEE Transactions on Nuclear Science*, 51 (6): 3427–3434, 2004.

- 21. Matteo Cecchetto. *Experimental and simulation study of neutron-induced single event effects in accelerator environment and implications on qualification approach.* PhD thesis, Montpellier, 2021.

- Oliver Sim Brüning, Paul Collier, P Lebrun, Stephen Myers, Ranko Ostojic, John Poole, and Paul Proudlock. *LHC Design Report*. CERN Yellow Reports: Monographs. CERN, Geneva, 2004. doi: https://doi.org/10.5170/CERN-2004-003-V-1. URL https://cds.cern.ch/ record/782076

- 23. Rubén García Alía, Markus Brugger, Francesco Cerutti, Salvatore Danzeca, Alfredo Ferrari, Simone Gilardoni, Yacine Kadi, Maria Kastriotou, Anton Lechner, Corinna Martinella, et al. LHC and HL-LHC: Present and future radiation environment in the high-luminosity collision points and rha implications. *IEEE Transactions on Nuclear Science*, 65 (1): 448–456, 2017.

- 24. Kacper Biłko, Cristina Bahamonde Castro, Markus Brugger, Rubén García Alía, Yacine Kadi, Anton Lechner, Giuseppe Lerner, and Oliver Stein. Radiation environment in the LHC Arc sections during run 2 and future HL-LHC operations. *IEEE Transactions on Nuclear Science*, 67 (7): 1682–1690, 2020.

- 25. Oliver Stein, Kacper Bilko, Markus Brugger, Salvatore Danzeca, Diego Di Francesca, R Garcia Alia, Yacine Kadi, G Li Vecchi, Corinna Martinella, et al. A systematic analysis of the prompt dose distribution at the large hadron collider. In *9th Int. Particle Accelerator Conf. (IPAC'18), Vancouver, BC, Canada, April 29-May 4, 2018*, pages 2036–2038. JACOW Publishing, Geneva, Switzerland, 2018.

- 26. Andrea Coronetti, Rubén García Alía, Jan Budroweit, Tomasz Rajkowski, Israel Da Costa Lopes, Kimmo Niskanen, Daniel Söderström, Carlo Cazzaniga, Rudy Ferraro, Salvatore Danzeca, et al. Radiation hardness assurance through system-level testing: Risk acceptance, facility requirements, test methodology, and data exploitation. *IEEE Transactions on Nuclear Science*, 68 (5): 958–969, 2021.

- 27. Ygor Aguiar, Andrea Apollonio, Giuseppe Lerner, Francesco Cerutti, Marta Sabaté-Gilarte, Salvatore Danzeca, Daniel Prelipcean, and Ruben García Alía. Radiation to electronics impact on CERN LHC operation: Run 2 overview and HL-LHC outlook. 2021.

- Ygor Aguiar, Andrea Apollonio, Giuseppe Lerner, Matteo Cecchetto, Jean-Baptiste Potoine, Matteo Brucoli, Salvatore Danzeca, Ruben García Alía, Kacper Biłko, Alessandro Zimmaro, et al. Implications and mitigation of radiation effects on the CERN SPS operation during 2021. *JACoW IPAC*, 2022: 740–743, 2022.

- 29. FLUKA website. https://fluka.cern

- G. Battistoni et al. Overview of the FLUKA code. Annals Nucl. Energy, 82: 10–18, 2015. doi: https://doi.org/10.1016/j.anucene.2014.11.007.

- 31. T. Böhlen et al. The FLUKA Code: Developments and Challenges for High Energy and Medical Applications. *Nuclear Data Sheets*, 120: 211–214, 06 2014. doi: https://doi.org/10. 1016/j.nds.2014.07.049.

- 32. R Garcia Alia et al. Radiation fields in high energy accelerators and their impact on single event effects. *Diss. Montpellier U*, 2014.

- 33. MP King, RA Reed, RA Weller, MH Mendenhall, RD Schrimpf, BD Sierawski, AL Sternberg, B Narasimham, JK Wang, E Pitta, et al. Electron-induced single-event upsets in static random access memory. *IEEE Transactions on Nuclear Science*, 60 (6): 4122–4129, 2013.

- 34. Maris Tali, Rubén García Alía, Markus Brugger, Veronique Ferlet-Cavrois, Roberto Corsini, Wilfrid Farabolini, Ali Mohammadzadeh, Giovanni Santin, and Ari Virtanen. High-energy electron-induced SEUs and Jovian environment impact. *IEEE Transactions on Nuclear Science*, 64 (8): 2016–2022, 2017.

- 35. Pablo Caron, Christophe Inguimbert, Laurent Artola, Nathalie Chatry, Nicolas Sukhaseum, Robert Ecoffet, and Françoise Bezerra. Physical mechanisms inducing electron single-event upset. *IEEE Transactions on Nuclear Science*, 65 (8): 1759–1767, 2018.

- 36. Pablo Caron, Christophe Inguimbert, Laurent Artola, Françoise Bezerra, and Robert Ecoffet. Role of electron-induced coulomb interactions to the total SEU rate during earth and juice missions. *IEEE Transactions on Nuclear Science*, 68 (8): 1607–1612, 2021.

- 37. Kenneth P Rodbell, David F Heidel, Henry HK Tang, Michael S Gordon, Phil Oldiges, and Conal E Murray. Low-energy proton-induced single-event-upsets in 65 nm node, silicon-oninsulator, latches and memory cells. *IEEE Transactions on Nuclear Science*, 54 (6): 2474– 2479, 2007.

- Rubén García Alía, Maris Tali, Markus Brugger, Matteo Cecchetto, Francesco Cerutti, Andrea Cononetti, Salvatore Danzeca, Luigi Esposito, Pablo Fernández-Martínez, Simone Gilardoni, et al. Direct ionization impact on accelerator mixed-field soft-error rate. *IEEE Transactions on Nuclear Science*, 67 (1): 345–352, 2019.

- 39. Andrea Coronetti, Rubén Garcia Alìa, Jialei Wang, Maris Tali, Matteo Cecchetto, Carlo Cazzaniga, Arto Javanainen, Frédéric Saigné, and Paul Leroux. Assessment of proton direct ionization for the radiation hardness assurance of deep submicron srams used in space applications. *IEEE Transactions on Nuclear Science*, 68 (5): 937–948, 2021.

- 40. James F Ziegler, Matthias D Ziegler, and Jochen P Biersack. Srim-the stopping and range of ions in matter (2010). Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms, 268 (11–12): 1818–1823, 2010.

- 41. RC Alig and S Bloom. Electron-hole-pair creation energies in semiconductors. *Physical review letters*, 35 (22): 1522, 1975.

- 42. Yatendra Pal Varshni. Temperature dependence of the energy gap in semiconductors. *Physica*, 34 (1): 149–154, 1967.

- 43. Robert C Baumann. Radiation-induced soft errors in advanced semiconductor technologies. *Device and Materials Reliability, IEEE Transactions on*, 5 (3): 305–316, 2005.

- 44. SM Sze and Kwok K Ng. Physics of semiconductor devices, John Wiley & Sons. *New York*, 68, 1981.

- 45. O. A. Amusan, A. F. Witulski, L. W. Massengill, B. L. Bhuva, P. R. Fleming, M. L. Alles, A. L. Sternberg, J. D. Black, and R. D. Schrimpf. Charge collection and charge sharing in a 130 nm cmos technology. *IEEE Transactions on Nuclear Science*, 53 (6): 3253–3258, Dec 2006. ISSN 0018-9499. doi: https://doi.org/10.1109/TNS.2006.884788.

- 46. B. Liu, S. Chen, B. Liang, Z. Liu, and Z. Zhao. Temperature dependency of charge sharing and mbu sensitivity in 130-nm cmos technology. *IEEE Transactions on Nuclear Science*, 56 (4): 2473–2479, Aug 2009. ISSN 0018-9499. doi: https://doi.org/10.1109/TNS.2009.2022267.

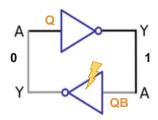

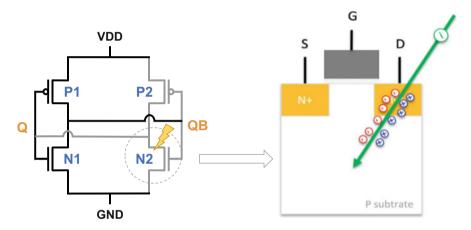

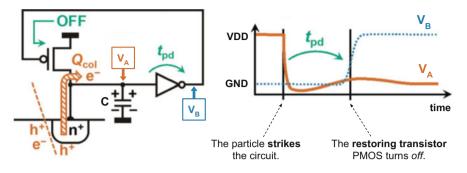

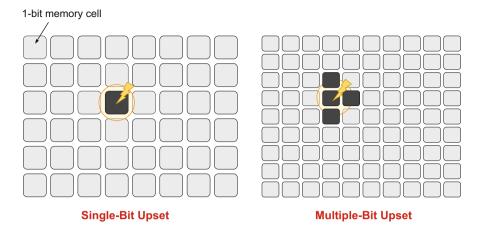

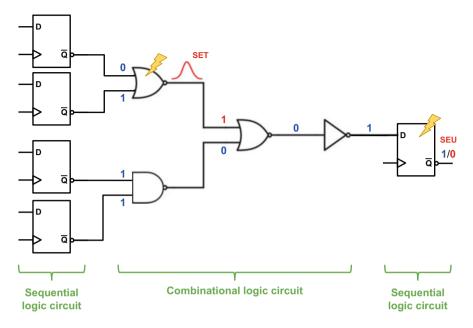

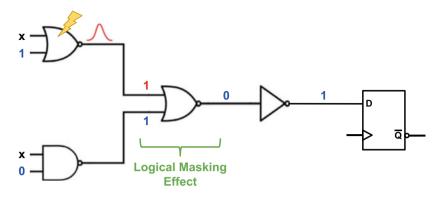

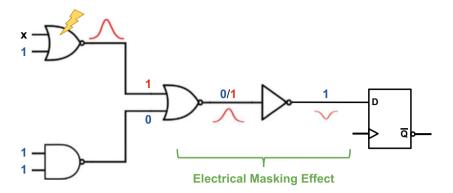

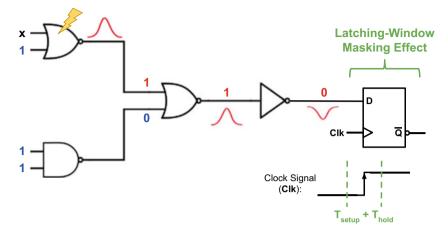

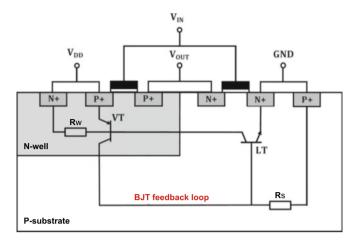

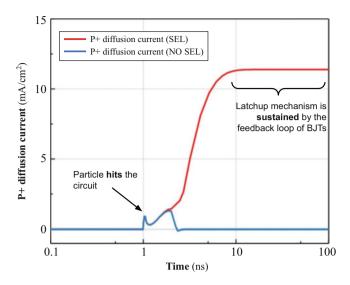

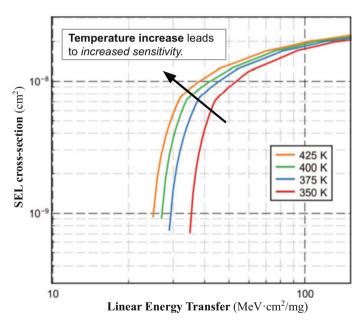

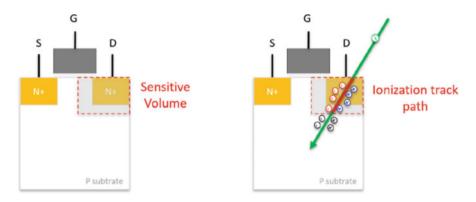

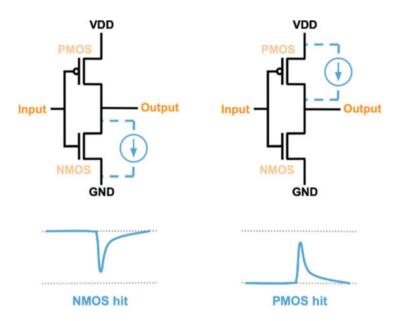

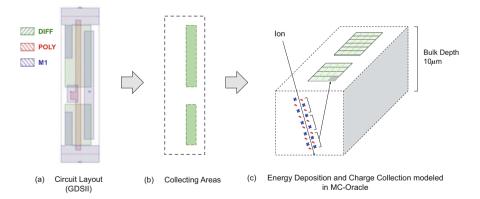

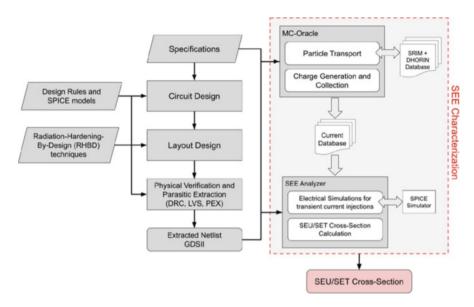

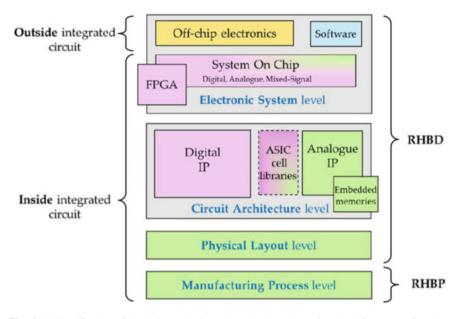

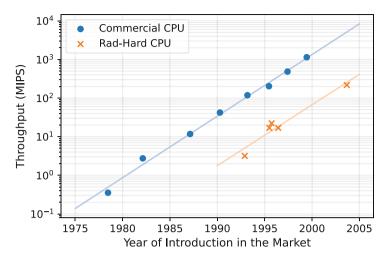

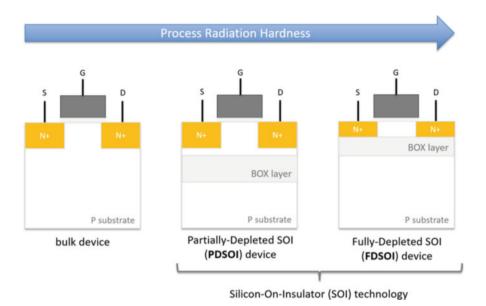

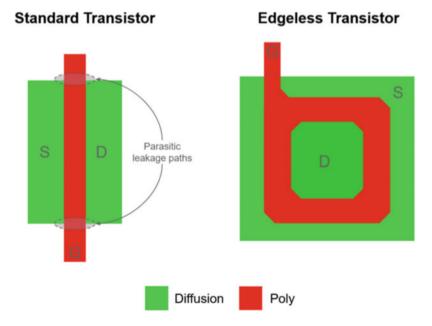

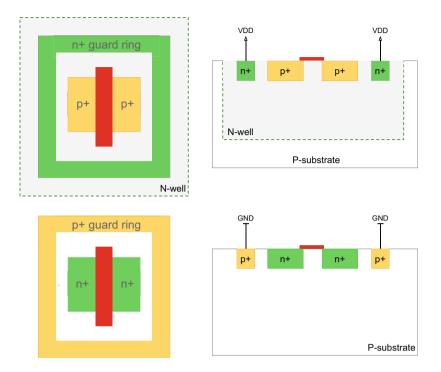

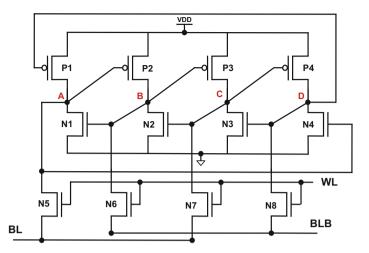

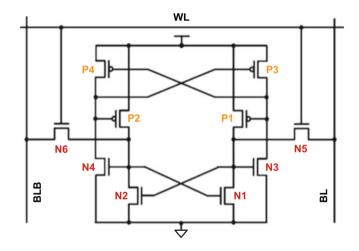

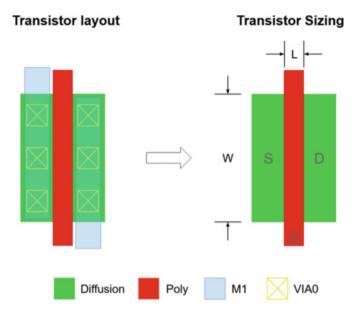

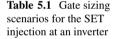

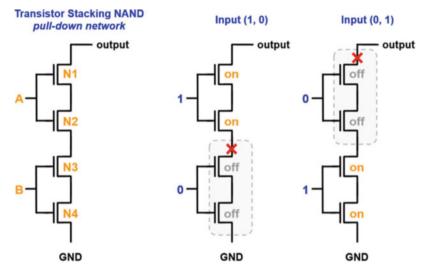

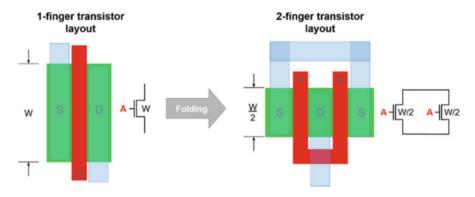

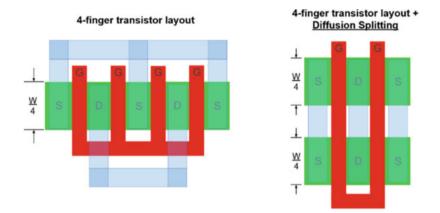

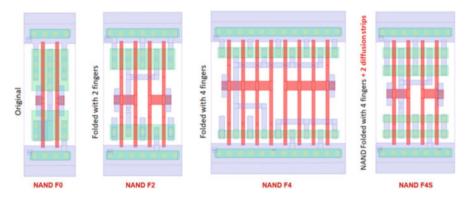

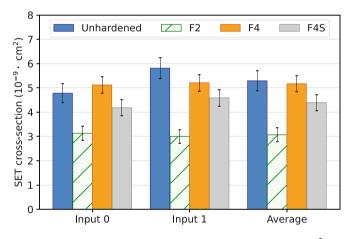

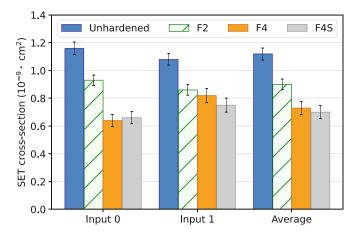

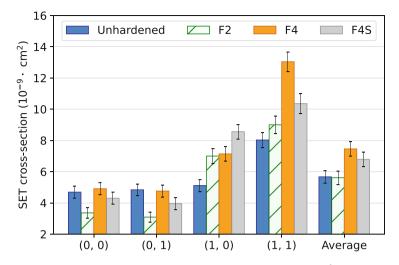

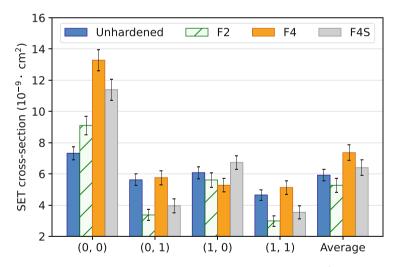

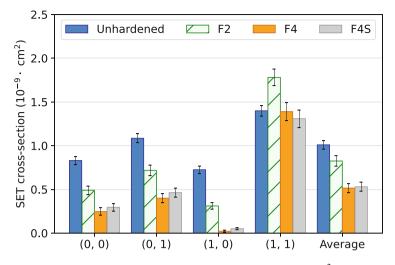

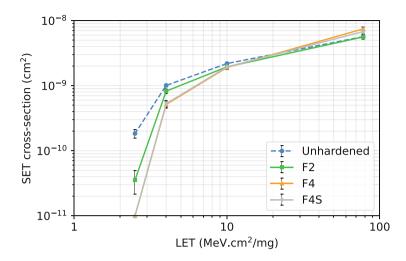

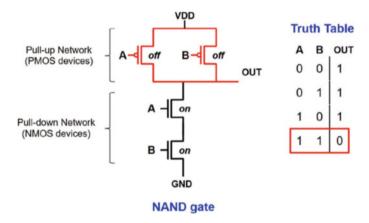

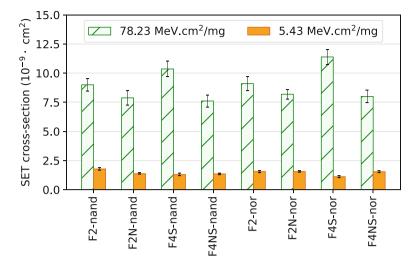

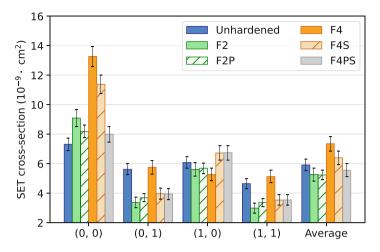

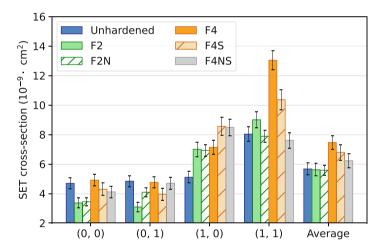

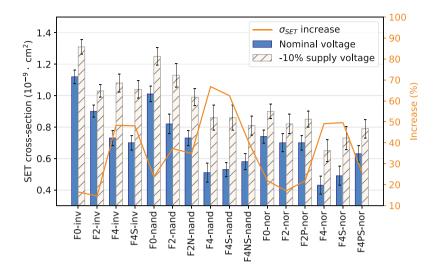

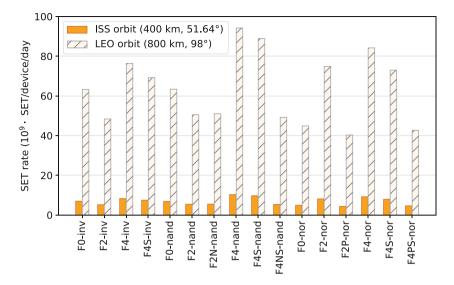

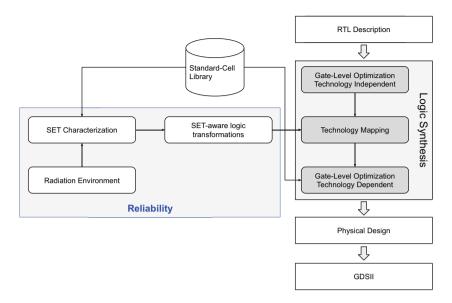

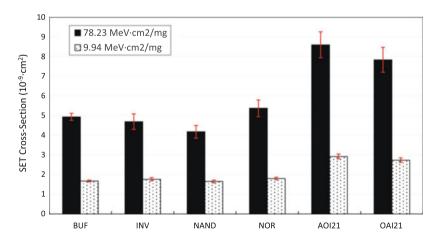

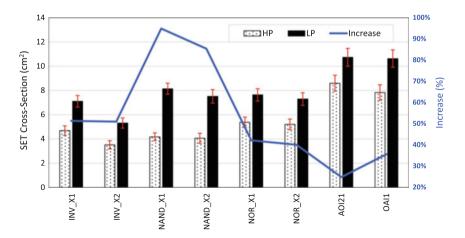

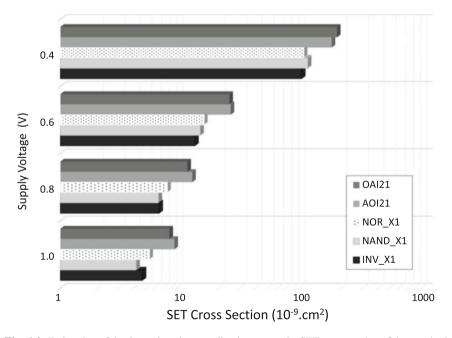

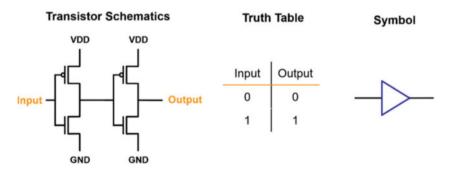

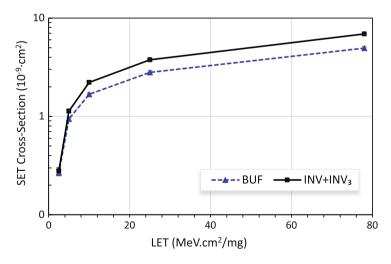

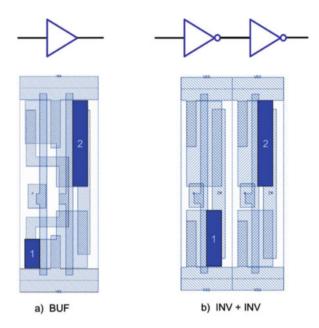

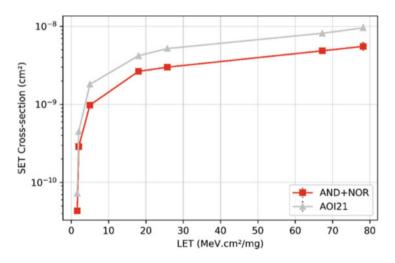

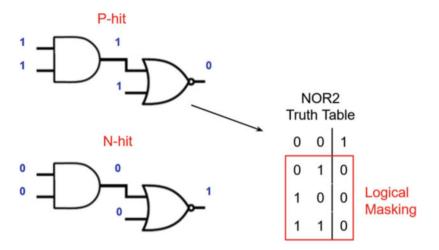

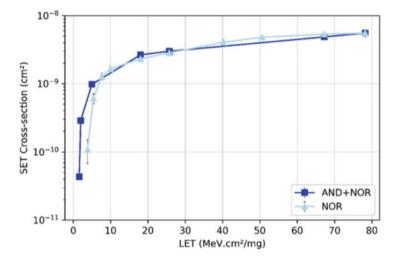

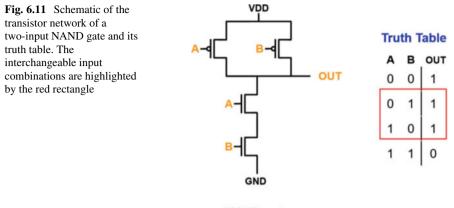

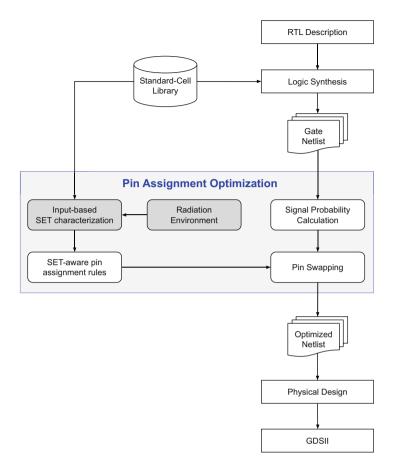

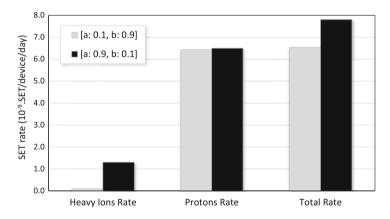

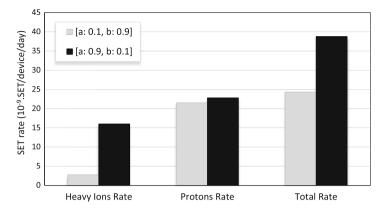

- 47. J. R. Ahlbin, L. W. Massengill, B. L. Bhuva, B. Narasimham, M. J. Gadlage, and P. H. Eaton. Single-event transient pulse quenching in advanced cmos logic circuits. *IEEE Transactions on Nuclear Science*, 56 (6): 3050–3056, Dec 2009. ISSN 0018-9499. doi: https://doi.org/10.1109/ TNS.2009.2033689.